## Parallelism

Parallelism: execute multiple operations simultaneously

### **Some Types**

- --- Instruction-Level Parallelism ===> execute multiple instructions from same job (ILP)

- --- Data Parallelism ===> operate on multiple data items from same job (SIMD, MIMD, SPMD)

- --- Thread-Level Parallelism ===> execute multiple jobs but same program

- --- Task-Level Parallelism ===> execute multiple jobs, multiple programs

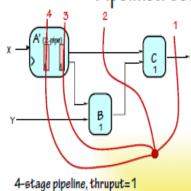

## ILP, Pipeline

Perf =

$$\frac{n \text{ instructions}}{\text{time}} = \frac{n}{n \text{ cpI}(1/c_R)} = \frac{CR}{cPI}$$

CR  $\Rightarrow$  perf

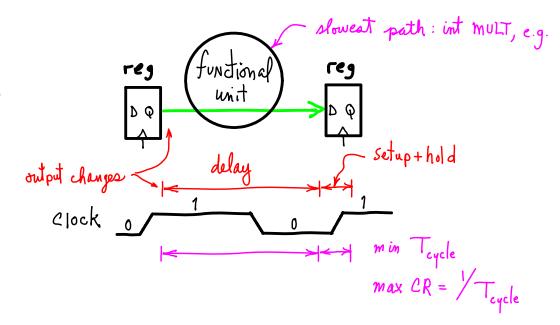

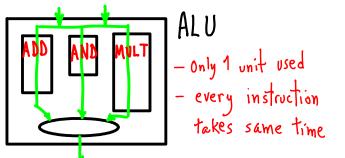

### CR limited by slowest path.

- --- Other, faster units could be clocked faster.

- --- But cannot because of slow path.

- --- Faster units waiting/idle.

Amdahl's Law says attack the common case. Every instruction faster w/ increased CR.

- --- MULT chopped into k fast pieces.

- --- More cycles for MULT, but faster CR.

also, see if we can get k pieces of MULT to run in Parallel

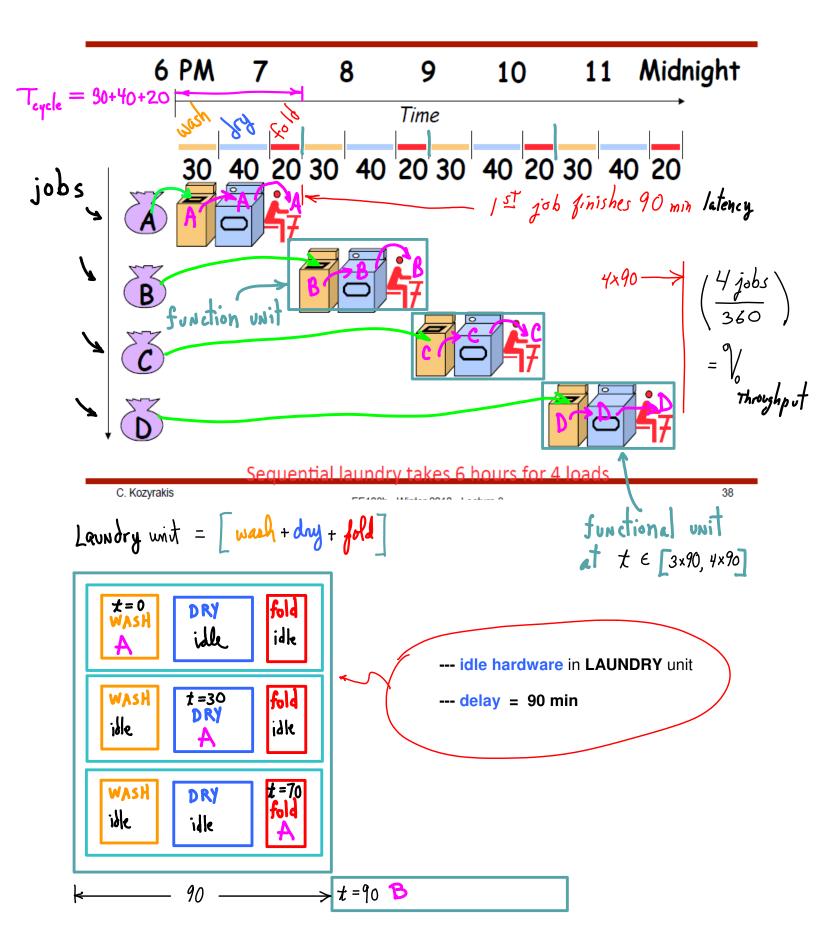

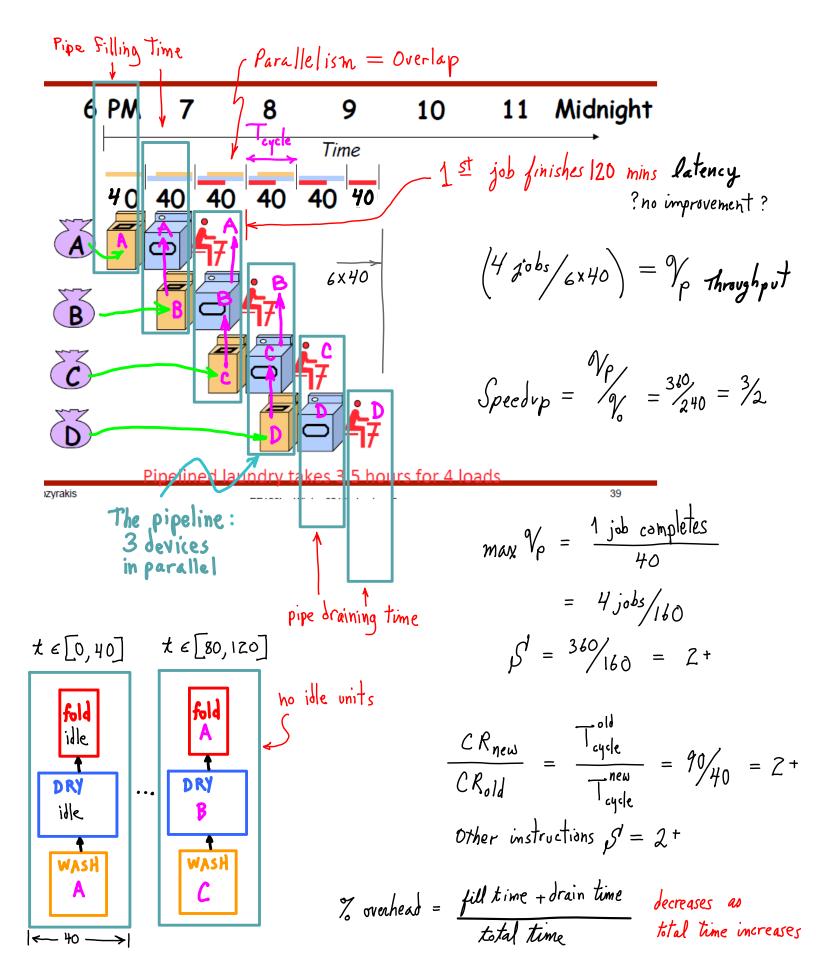

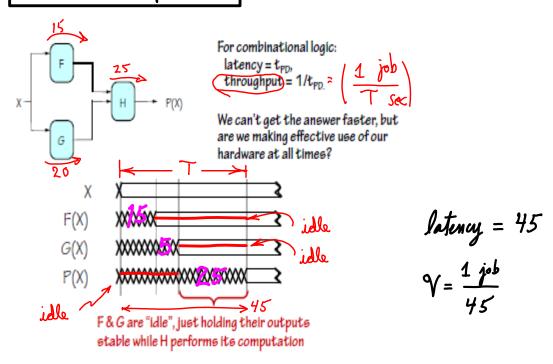

# Sequential: 1-piece functional unit

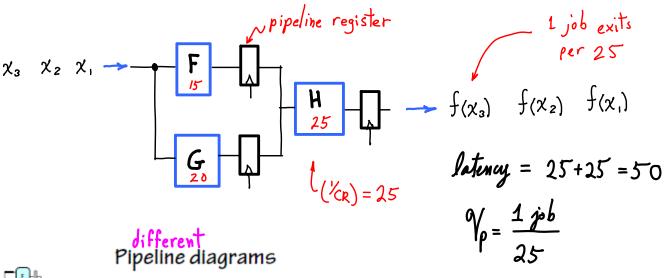

# Pipelined: pipelined functional unit

## General pipelines

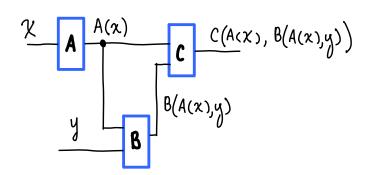

# Bad pipelining

What's wrong? How to fix?

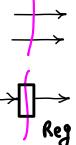

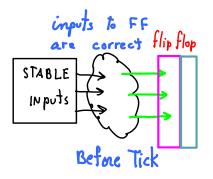

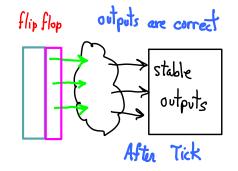

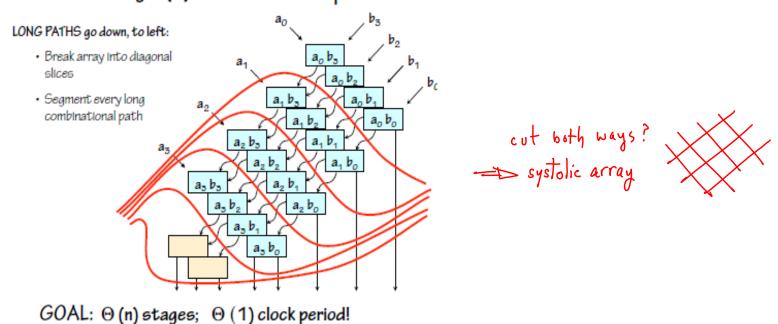

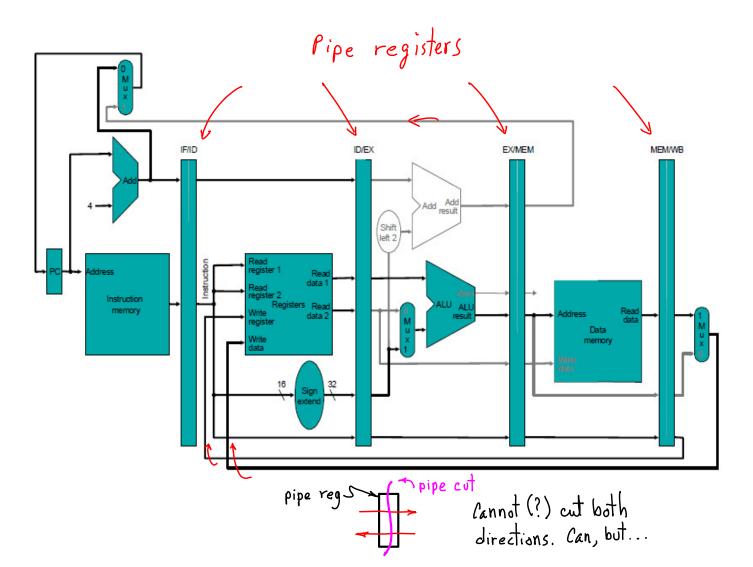

### General Method

Cut all paths in same direction bisect graph

===> cut set

For each cut add Reg to path

balance stage delays

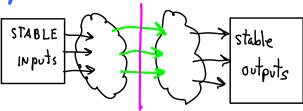

# Inductive proof

signals in cut-set are cornect

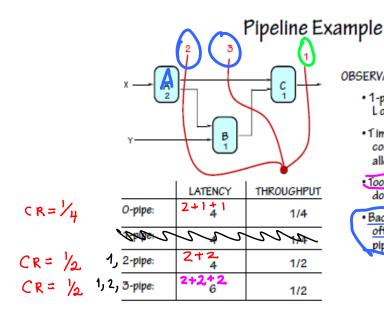

#### OBSERVATIONS:

- 1-pipeline improves neither Lor T.

- Timproved by breaking long combinational paths, allowing faster clock.

- · Too many stages cost don't improve T.

- Back-to-back registers are often required to keep pipeline well-formed.

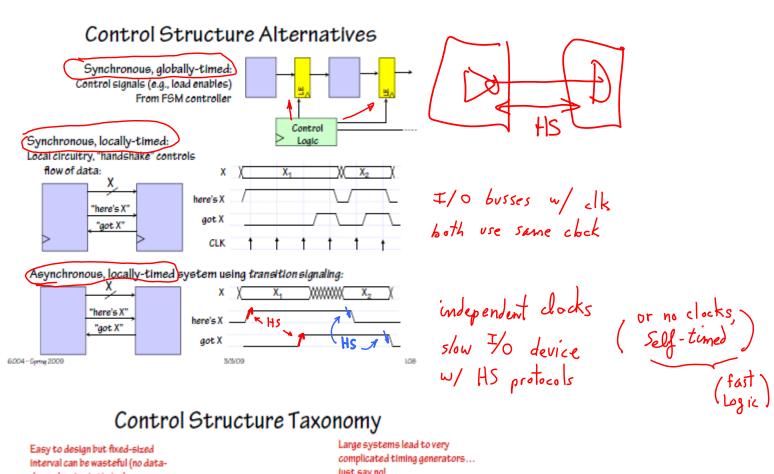

Pipelined systems can be hierarchical:

- · Replacing a slow combinational component with a k-pipe version may Increase clock frequency

- · Must account for new pipeline stages in our plan

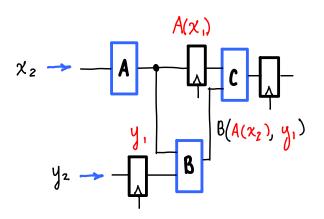

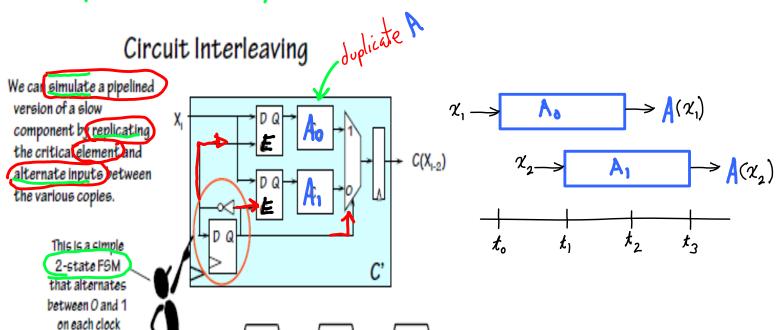

## Can't split A in two w/ T=1? Fake it!

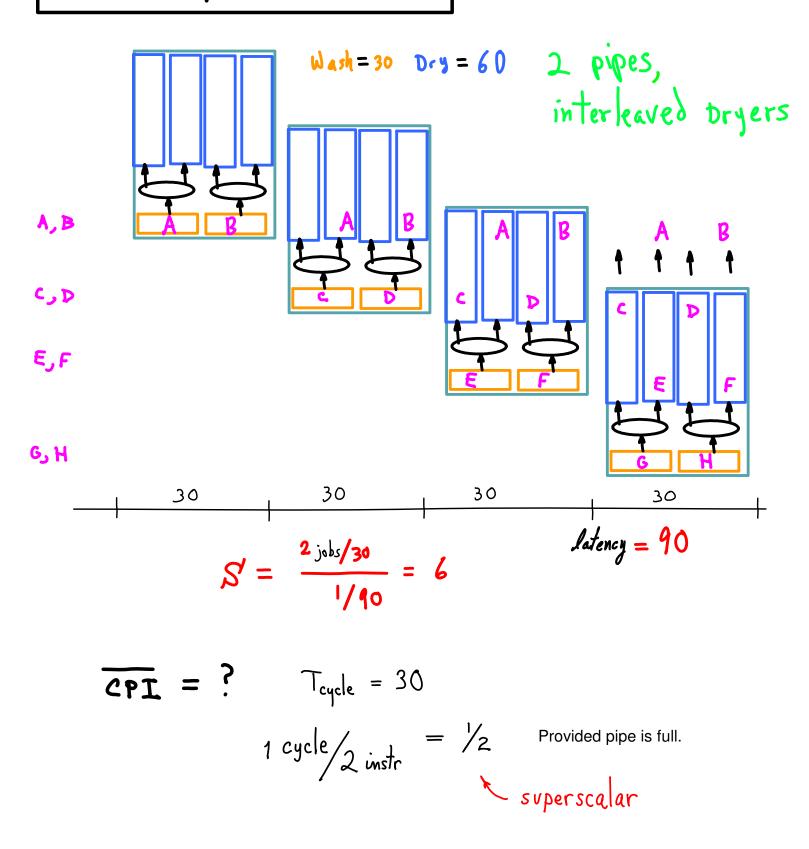

# Parallel pipes + interleave

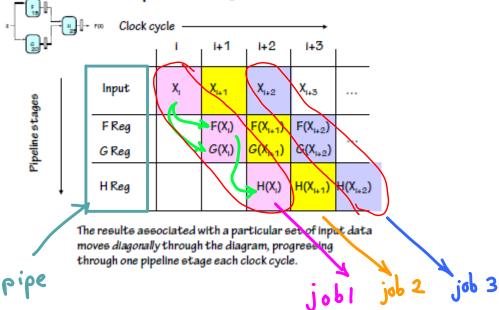

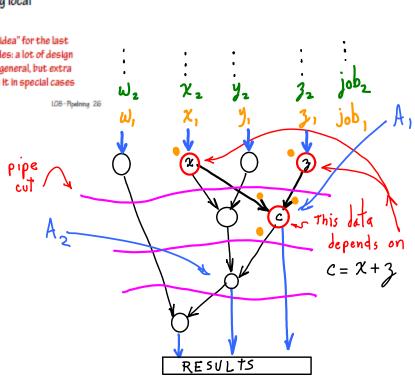

### **Data Dependency Graphs** and **Pipelining**

- --- Entire algorithm is dependency graph

- --- Data-Flow: nodes fire when inputs ready

- --- Multiple jobs

- --- High throughput

- --- Is parallelism as high as possible?

- --- Does timing depend on data?

### Breaking O(n) combinational paths

004-Serina 2009 3/5/09 L09-Multieli

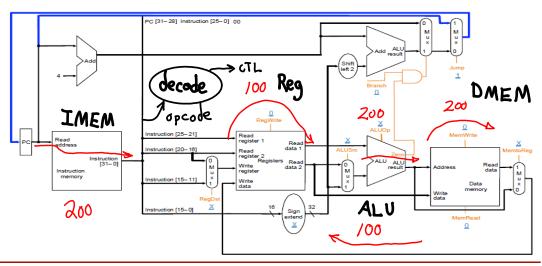

### 1-cycle MIPS processor

- --- Harvard Architecture (two memories)

- --- clocking PC initiates cycle

### Single Cycle Processor Performance

Functional unit delay

- Memory: 200ps

ALU and adders: 200ps

- Register file: 100 ps

105 = 10 -12 sec

| Instruction<br>Class | Instruction memory | Register<br>read | ALU<br>operation | Data<br>memory | Register<br>write | Total |

|----------------------|--------------------|------------------|------------------|----------------|-------------------|-------|

| R-type               | 200                | 100              | 200              |                | 100               | 600   |

| load                 | 200                | 100              | 200              | 200            | 100               | 800   |

| store                | 200                | 100              | 200              | 200            |                   | 700   |

| branch               | 200                | 100              | 200              |                |                   | 500   |

| jump                 | 200                |                  |                  |                |                   | 200   |

max delay = Tolock

$\frac{1}{T_{hel}} = \frac{1}{0.8\pi} = 1.25 GH_Z$

CPU clock cycle = 800 ps = 0.8ns (1.25GHz)

what if we let clock trigger delay by opcode?

|                         |                      |                       |                  | 90               |                |                   |       |

|-------------------------|----------------------|-----------------------|------------------|------------------|----------------|-------------------|-------|

| Instruction Mix 45% ALU | Instruction<br>Class | Instruction<br>memory | Register<br>read | ALU<br>operation | Data<br>memory | Register<br>write | Total |

| ∠ 25% loads             |                      |                       |                  |                  |                |                   |       |

25% loads 100 200 100 600 R-type 200 10% stores load 100 200 15% branches 700 store 200 100 200 200 5% jumps 100 200 500 branch 200

> 0.6 ns 0.8 0.7

0.5

• CPU clock cycle =  $0.6 \times 45\% + (0.8 \times 25\% + (0.7 \times 10\% + (0.5 \times 15\% + (0.2 \times 5\%))$

= 0.625 ns (1.6 GHz)

=> 1.6 GHz

speedup?  $\int_{\text{new-old}}^{1.6} = 1.6 = 1.28$

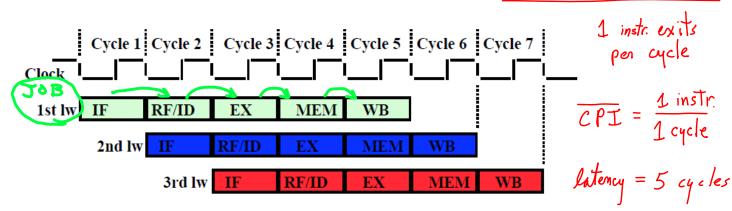

## Pipelining Load $l\omega$

- Load instruction takes 5 stages

- Five independent functional units work on each stage

- · Each functional unit used only once

- Another load can start as soon as 1st finishes IF stage

- Each load still takes 5 cycles to complete

- The throughput, however, is much higher

when all stages busy

# Max out pipeling?

$$delay \rightarrow \frac{delay}{n} \longrightarrow CR \rightarrow n \times CR \quad (n \rightarrow \infty?)$$

NO:

- small operations harder to divide into pieces

- nxCR - nx Power

≈ 20 stages limit for CPU (But elsewhere?)