LC3-uArch-MemMapIOstacksINT

OS Trap routines defined in PP's OS. (You could add to these, if you wanted to rewrite the OS.)

| TRAP x25HALTTRAP x20GETCTRAP x20GETCTRAP x21OUTTRAP x22PUTSTRAP x23INTRAP x24PUTSPTRAP x24PUTSP | TRAP <n></n> | Assembly-psuedonymn Description |                                                                                       |

|-------------------------------------------------------------------------------------------------|--------------|---------------------------------|---------------------------------------------------------------------------------------|

|                                                                                                 | TRAP x20     | GETC                            | one char in, keyboard data ==> R0[7:0] (clears R0 first).                             |

|                                                                                                 | TRAP x21     | OUT                             | one char out, R0[7:0] ==> display, ignores big-end byte, R0[15:8].                    |

|                                                                                                 | TRAP x22     | PUTS                            | string out, Mem[R0++] ==> display until x0000. Ignore big-end bytes, 1 char per word. |

|                                                                                                 | TRAP x23     | IN                              | displays prompt, then one char in ala GETC.                                           |

See PP, Append. A.4, Table A.2

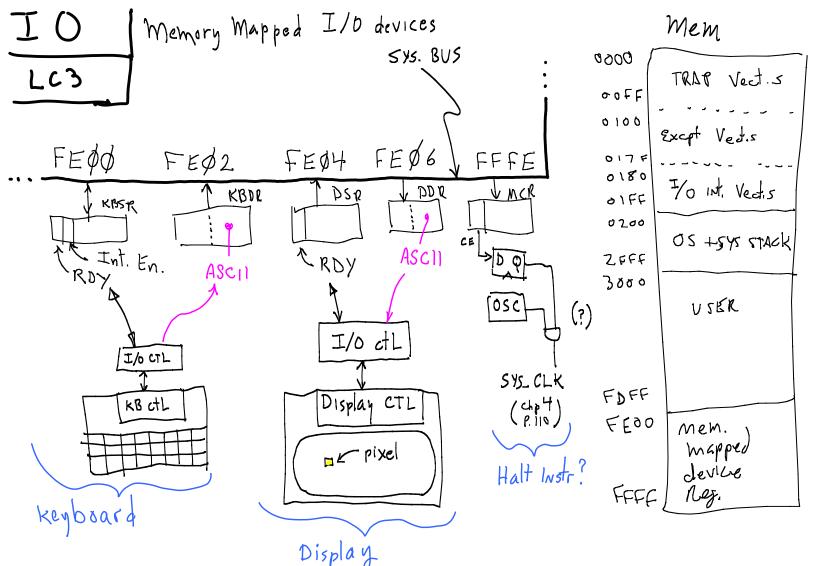

I/O Device hardware communication layers

-----

(0.) device's onboard controller

communicates with

(1.) device's bus interface board (aka "device controller"),

communicates with

(2.) I/O bus (PCI bus, for example).

communicates with

(3.) CPU's memory/bus unit

Device controllers are "programmed" by sending control words to their "device registers". Device status information is returned, and data is sent/received to/from the device via the device data registers. Device registers are accessed via memory LD/ST instructions using memory addresses (memory-mapped I/O).

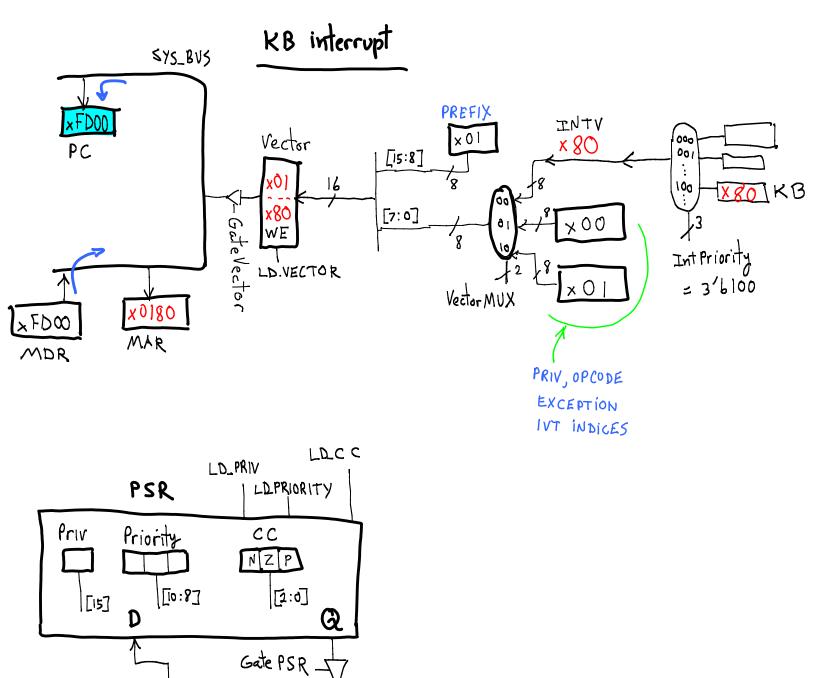

LC3 FSM READ states:

33, 28, 24, 25, 29, 36, 40, 52\*

LC3 FSM WRITE states: 16, 41\*, 48\*

\* Interrupt mechanism not implemented in LC3simulate.exe

۱

入

СС

Logic

O

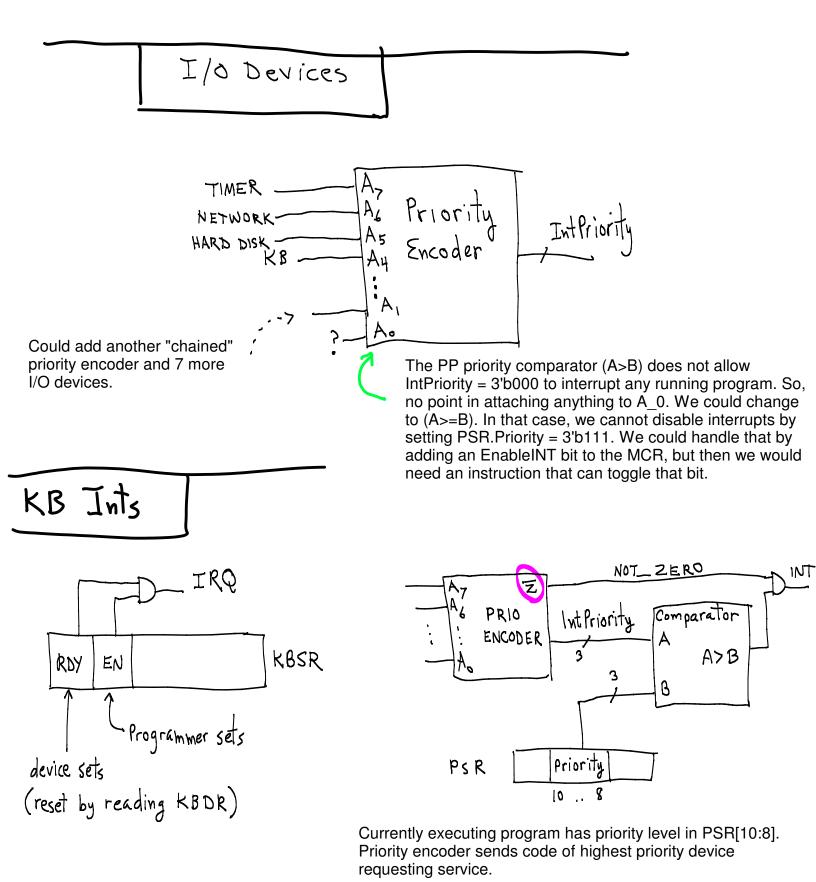

Int Priority

SetPriv

PSRMUX

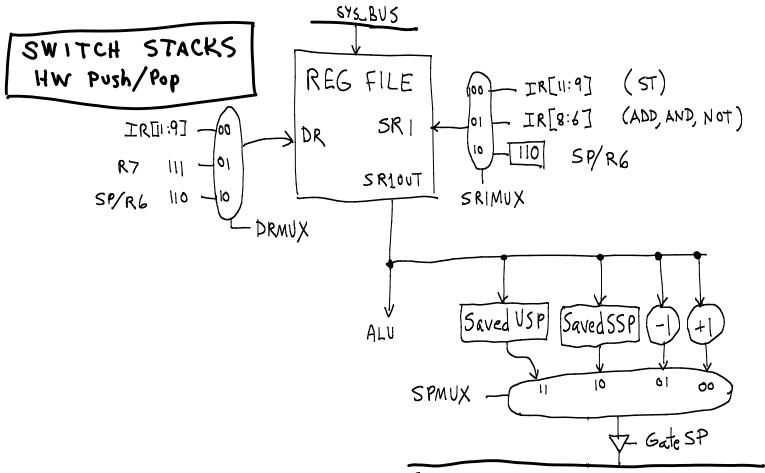

SYS\_BUS