See P&P Appendices A and C: LC3 Memory Map LC-3 ISA, TRAPS, Devices, Interrupts, Exceptions. Mem Mem UNIX LC3-05 0000 0000 VT VT Map Mem Map 05 USER addr ~ 16-bits -3000 8000 28 = 256 x 0000 USER 05 TRAP I/0 VECTORS I/0 FFFF FFFF XOOFF 27 = 128 X 0100 Vector Table, handware defined EXCEPTION • VECTORS X017F VT space: 0000-0200 = 2° '/2 k X0180 17 = 128 • INTERRUPT XOIFF VECTORS x 0200 OS Kernel ROUTINES BOOT OS space ٥٥\* • TRAP,  $3 \times 2^{12} = 12 k$ 0 - 3000EXCEPTION, INTERRUPT SPACE OS Data OS STACK x2FFF x 300 0 ≈64k-12k = 53k USER • SPACE xFFDF device address range. XFFEO I/O • Device 1111 1111 1110 0000 FFEO X F F FF Registers 1111 1111 1111 1111 FFFFN 5 bits → 32 registers If there bite, addr Bus [15:5], are all 1's. reference is to I/O device register, not memory. Memory ignores R/W request. Device responds.

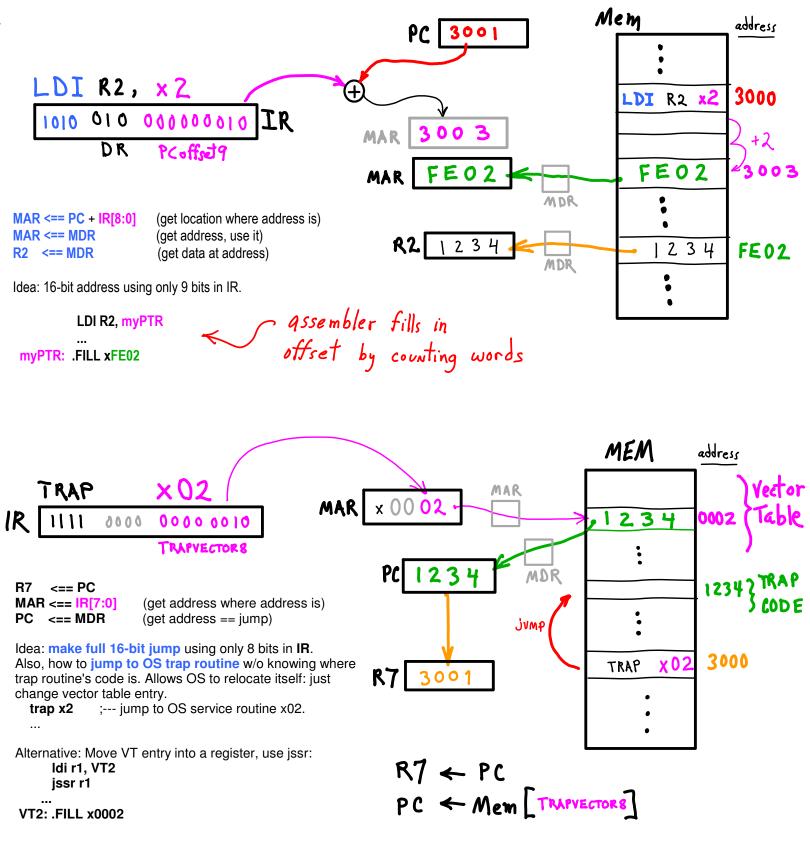

--- fetch address from location

--- R/W data to/from address OR jump to address

object

Aside: Using what we had above to eliminate ldi, we could eliminate both LDI and TRAP instructions from the LC3's ISA: we would have two unused opcodes to play with.

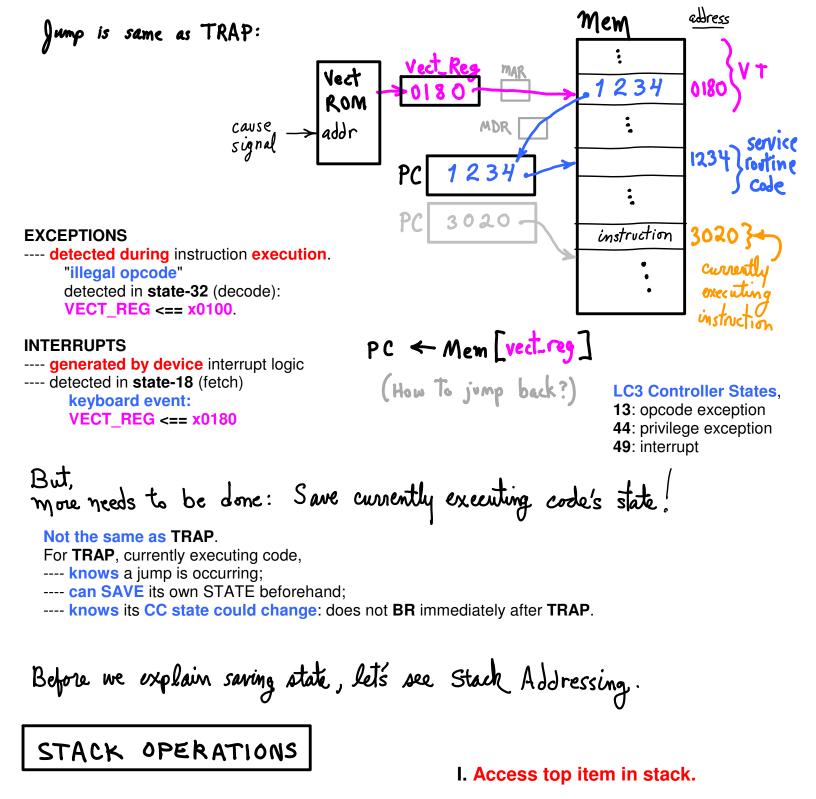

Exceptions Interrupts

Yet another address-in-memory mechanism. Just like **TRAP**, but not an instruction.

Something goes wrong: I/O device sends a signal: jump to OS routine, Exception jump to OS routine,

Interrupt

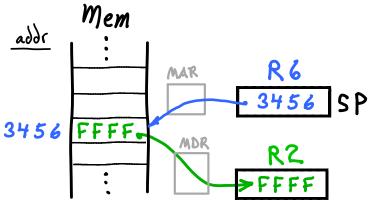

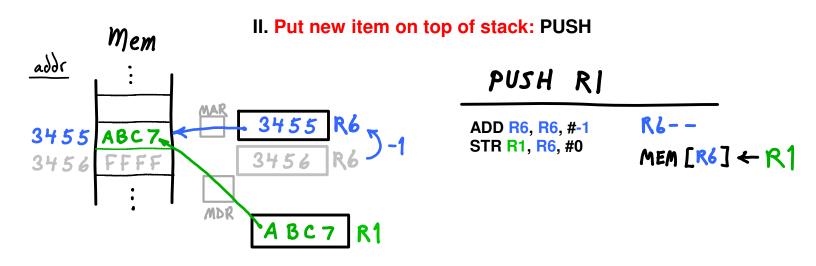

LDR R2, R6, #0

R2 <== MEM[ R6 ]

Stack Pointer (SP) is R6

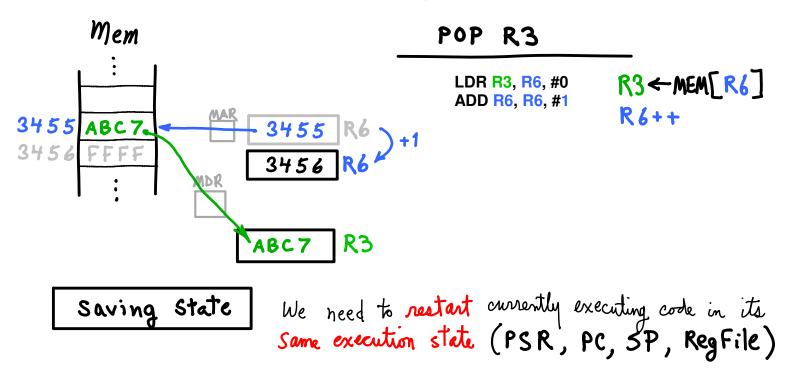

## When an exception/interrupt occurs

- ---- **PSR altered** immediately, before the next instruction is fetched.

- ---- PC altered, i.e., a jump.

PC could go to R7, but what is in R7 (function calls, nested interrupts)?

- ---- SP (R6) altered to push state, it needs to be saved.

- ---- Regs can be saved by service routine code.

- ===> Hardware, not instruction execution, must save state!

LC3 States for Interrupt

```

49 INT

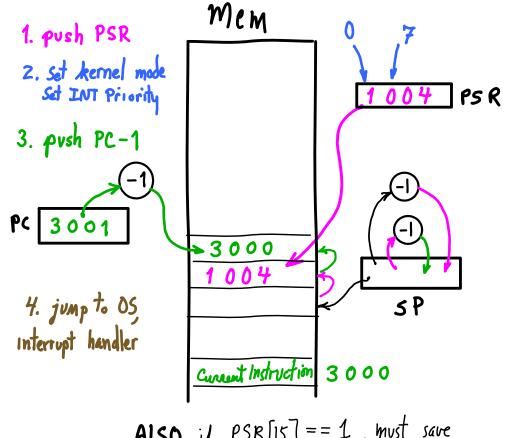

MDR <== PSR

PSR[10:8] <== 3'b111

PSR[15] <== 1'b0

<PSR[15] == 1?> save R6

```

```

37, 41 push PSR

SP <== SP-1

MAR <== SP-1

Mem <== MDR

43, 47, 48 push PC

MDR <== PC-1

SP <== SP-1

MAR <== SP-1

Mem <== MDR

50, 52, 54 jump

MAR <== Vector

MDR <== Mem

PC <== MDR

```

ALSO, if PSR[15] == 1, must save SP, and switch to SUPER'S STACK. See R6 save/restore handware near ALU.

## When exception/interrupt routine COMPLETES

- ---- **RESTORE Regs**, done in service routine execute **LD** instructions

- --- **RESTORE PC, PSR**, execute the **RTI** instruction:

## Pop PC

Pop PSR Restore SP (see R6 save/restore hardware)

SP