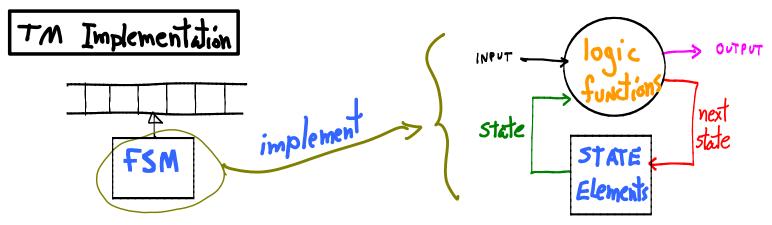

To build any TM, WE NEED:

- --- (1.) FSM: state logic functions (output and next-state)

- --- (2.) Tape: methods to R/W symbols, we'll use registers (RAM).

--- (3.) Symbol set = a set of fixed length bit strings, e.g.,  $S = \{0,1\}$ (2 symbols)  $S = \{00, 01, 10, 11\}$ (4 symbols)  $S = \{000, 001, 010, 011, 100, 101, 110, 111\}$ (8 symbols)

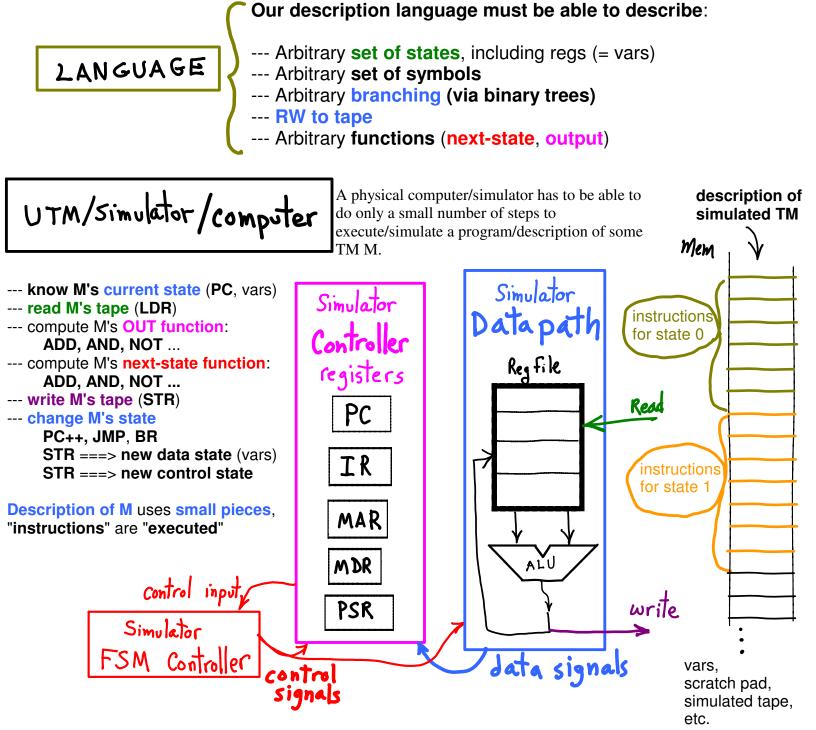

Our Computer/Simulator is a FSM. Our simulated machines are FSMs, too. Turing Complete/Universal (can simulate any TM) we need:

- --- a Language to describe any TM,

- --- a Simulator that understands that language.

We need to describe arbitrary TMs so that our computer/simulator can execute/simulate them.

We can build the machines physically. We need a language to describe them as well.

FSM Controller uses registers (e.g., PC) to remember:

- --- M's state (control + data states)

- --- symbols read (RegFile)

- --- symbols to write (RegFile)

- --- step of simulation (UTM's controller's state)

- --- partial steps of function evaluations (next-state, output) data registers, PSR, on tape, ...

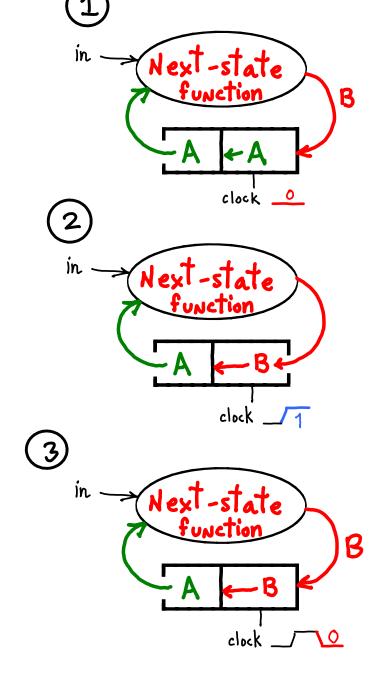

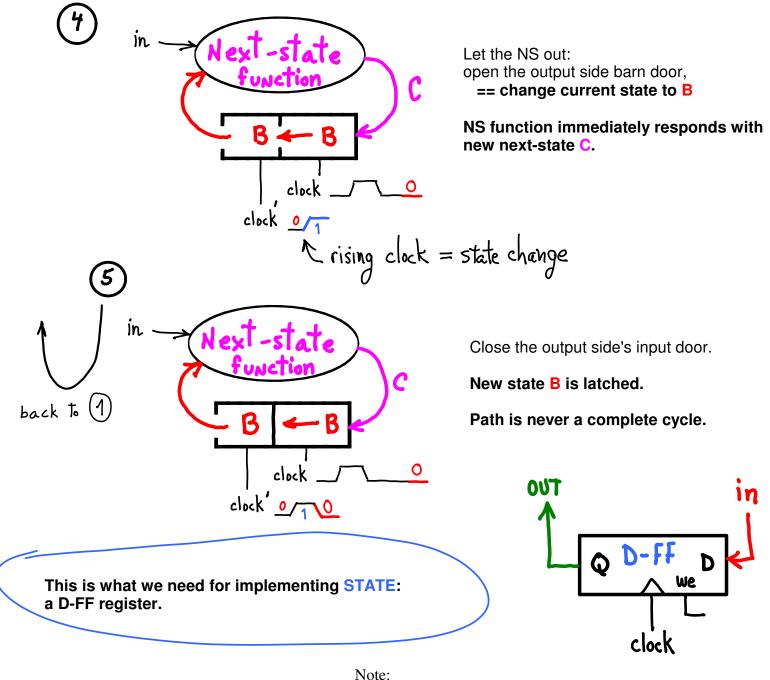

STATE ELEMENTS pos. cdge-triggered FF

Problem:

Katy bar the door

Feedback loop: state change, NS change, state change, NS change, ... State changes w/o control.

We want coordination w/ input data.

When the input is ready, Then allow a state change.

Input has to be stable for a minimum time.

Current state has to remain stable to get correct next state.

## Solution

Never allow a complete cycle path.

Break path at the state element.

1. Current state = **A**

2. Allow NS signal **B** in (read/sample state element input).

3. Then, close the barn door.B is captured, cannot be changed by changes in NS function output.

input "sampled" "latched"

We add a "write-enable" because sometimes we need to choose whether or not the register will change its value.

So far, for FSMs, our D-FFs are always write-enabled, we==1.

Two Ways to Specify a Function f(x)

| <ul> <li>(1)</li> <li>Describe how to evaluate f(x):</li> <li>E.g.</li> </ul> | (2)<br>Show a table of values of $f(x)$ :<br>E.g. |

|-------------------------------------------------------------------------------|---------------------------------------------------|

| f(x) = 2x                                                                     | $\begin{array}{ccc} x & f(x) \\ & \end{array}$    |

| (given any value x)                                                           | 0 1<br>1 0                                        |

(for every value of x)

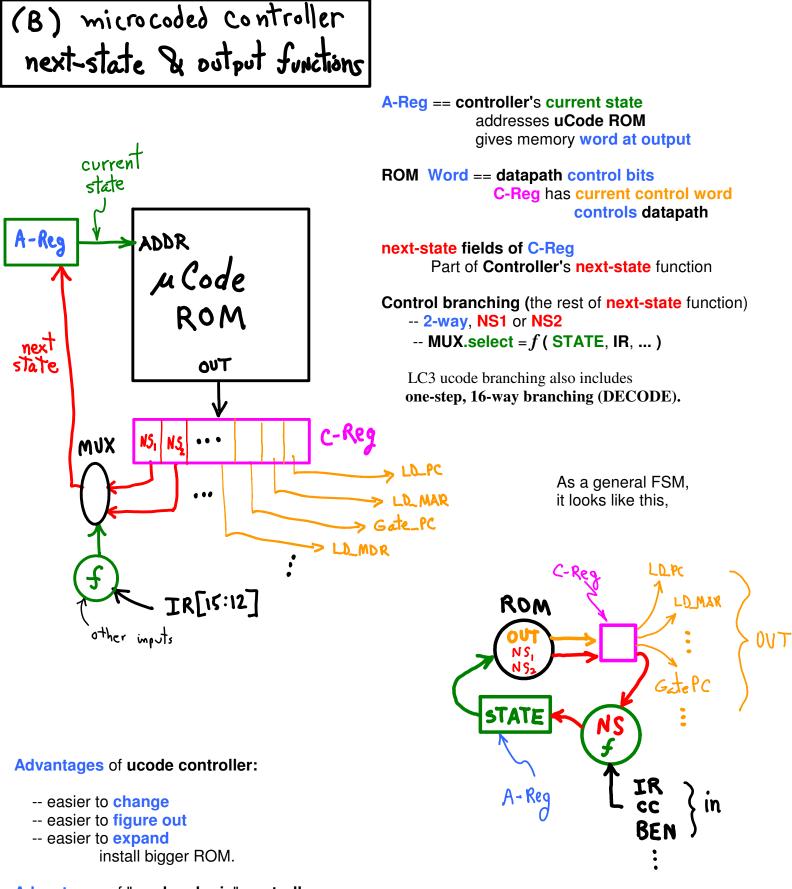

Advantages of "random logic" controller:

- -- faster

- -- smaller (?)

- -- distributed throughout machine

Caveat: The C-Reg is just to make the picture clearer, it doesn't actually exist in LC3. Instead, the ROM's outputs go directly to control inputs.

Suppose we have,

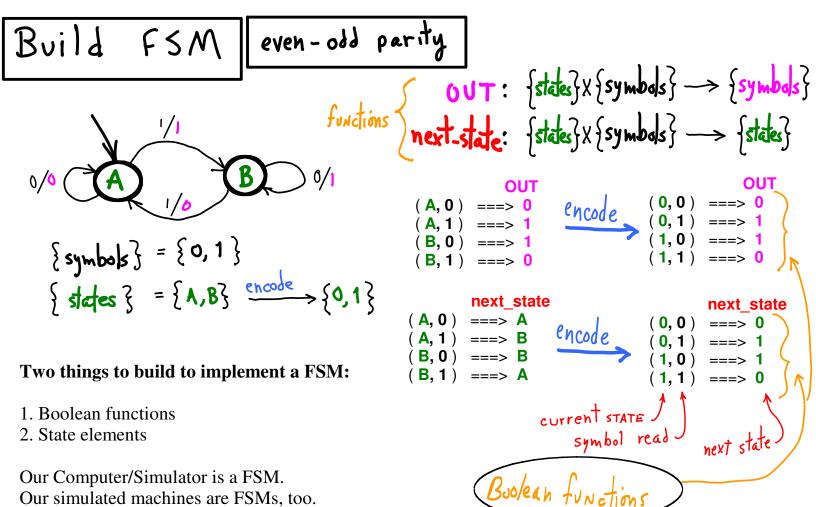

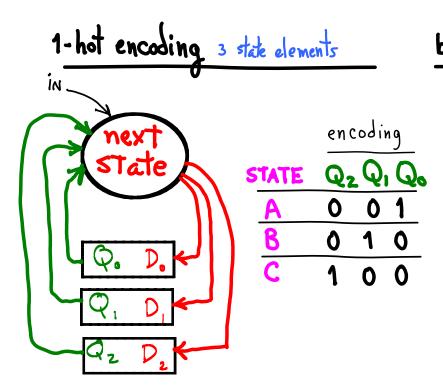

--- 1-bit state elements

--- 1-bit function elements

HOW do we put them together to implement a FSM M?

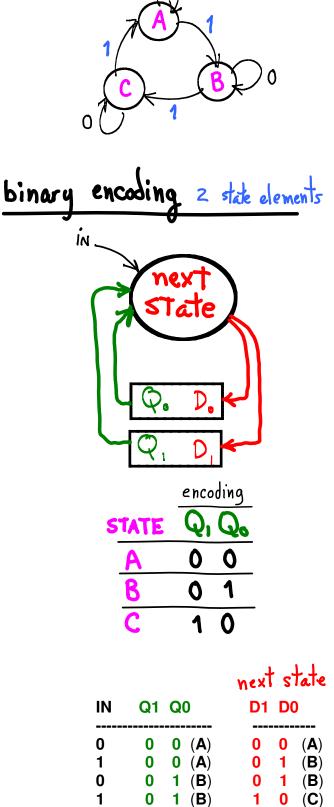

We need to **encode the states of M** in bits. We get **boolean functions** for **next-state function** (and **output** function).

The next-state function as a table:

| imput current state             |                            |                                 |              | f(x)<br>next state |                            |                                 |                            |                                        |

|---------------------------------|----------------------------|---------------------------------|--------------|--------------------|----------------------------|---------------------------------|----------------------------|----------------------------------------|

| IN                              | Q2 Q1 Q0                   |                                 |              | D2 D1 D0           |                            |                                 |                            |                                        |

| 0<br>1<br>0<br>1<br>0<br>1<br>* | 0<br>0<br>0<br>1<br>1<br>* | 0<br>0<br>1<br>1<br>0<br>0<br>* | 0 (I<br>0 (( |                    | 0<br>0<br>1<br>1<br>0<br>X | 0<br>1<br>1<br>0<br>0<br>0<br>X | 1<br>0<br>0<br>0<br>1<br>X | (A)<br>(B)<br>(B)<br>(C)<br>(C)<br>(A) |

\* rows that cannot be reached. X is for **don't care**, either 0 or 1.

E.g., mod-3 machine

\* rows cannot be reached.

X is for **don't care**: either 0 or 1.

**0** (**C**)

**0** (**C**)

1

0

Х

**0** (**C**)

**(A**)

0

Х

0

1

1

1

IF we have a universal language (able to describe any TM)

All we need to know is **How To Build**:

- --- 1-bit state elements?

- --- 1-bit functions?