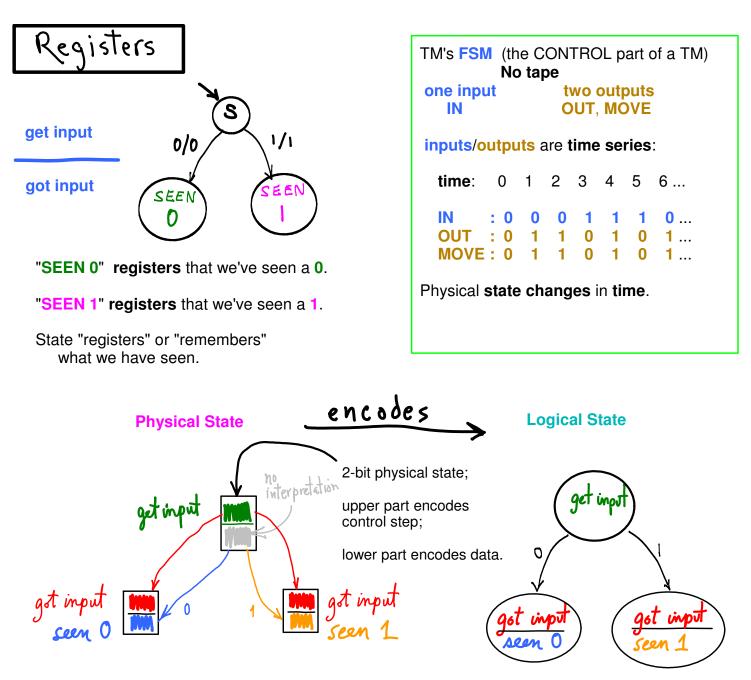

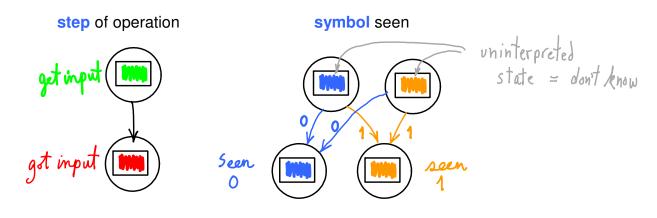

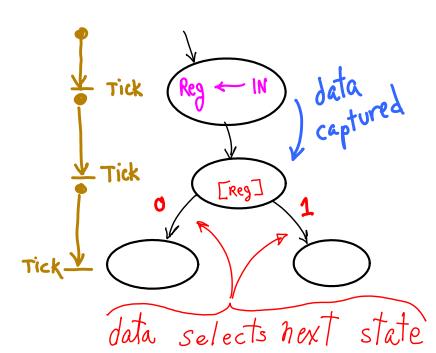

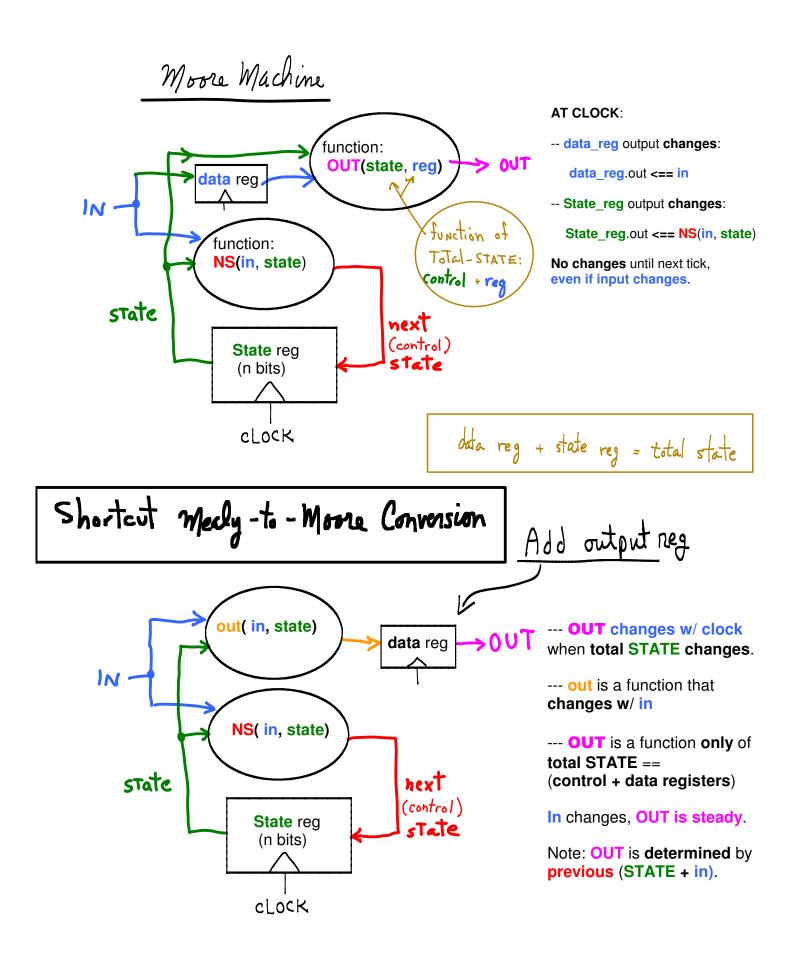

STATE can be thought of as consisting of two parts:

Before reading input ( "get-data" control state): we don't care which of upper 4 states we are in.

After reading, ("data-registered" control state) we are in one of 4 states, data is recorded.

32-bit data ==> 4G branches. We'd like to ignore data state, concentrate on control state.

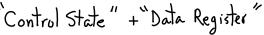

st<u>ate</u>

REG

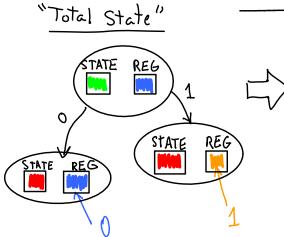

Complete state description:

--- ready-for-data-and-reg-is-zero,

--- got-data-and-reg-is-zero

--- got-data-and-reg-is-one

Control state description: --- get-data --- got-data

CTATE

REG

IN

Control Branching

**BIG IDEA:**

SPLIT TOTAL STATE into two parts:

--- 1. OPERATIONAL STATE Where we are in doing things

--- 2. DATA REGISTER STATE What we know at this point

registering a 32-bit input symbol :

(2 CONTROL states) X (4G data states)

versus

-- 2 CONTROL states (+ content of reg.)

Next CONTROL state depends on register content.

-- States === Register Transfers

-- Branches labeled w/ register content.

**CLOCK** causes:

- ---- register transfers

- ---- control state changes

REGISTERS for ---- CONTROL STATE ---- DATA

---- BOTH types change w/ CLOCK

We choose which part of data state is relevant, ignoring the rest.

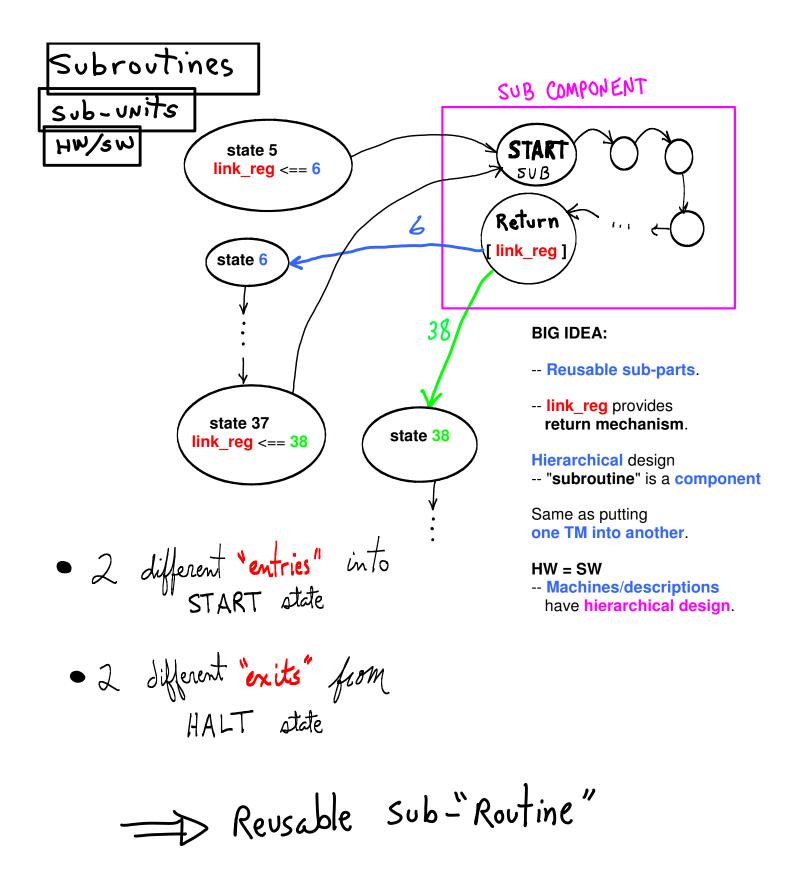

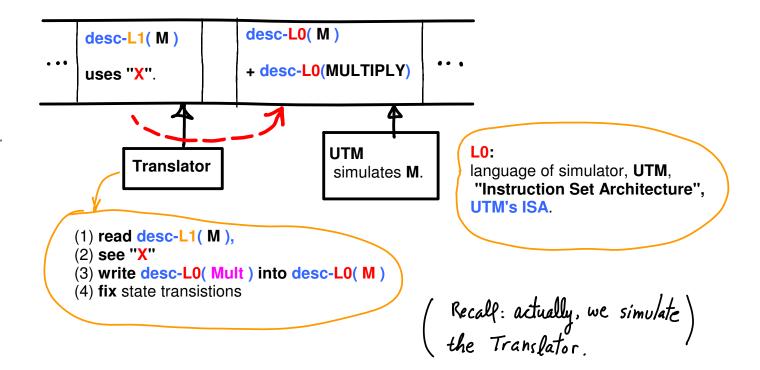

BIG IDEA: Extend simulator with additional hardware (hardware subroutines).

--- (A) simulated M's description has sub-routine, desc( MULTIPLY )

--- versus (B) add a symbol "X" to M's description

branch to a hardware MULTIPLY subroutine: ===> New Simulator is FASTER, ===> Desc(M) is SMALLER: desc( MULTIPLY ) is gone

--- Software == Hardware

Could we extend desc(M) in the same way?

"X" in desc( M )

Translator adds desc(MULTIPY) to desc(M)?

===> Libraries, code inserted where referenced.

--- Add layers of translation

scripting language ==> C++ ==> C ==> asm ==> ISA

--- Migrate subroutines down (maybe into UTM's hardware)

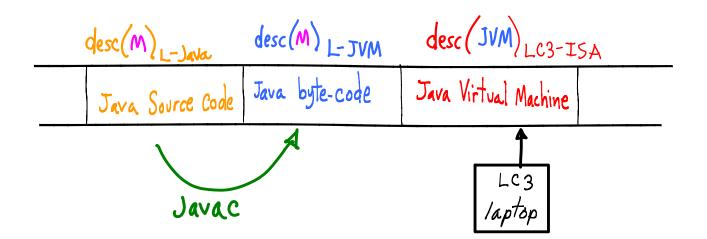

--- Simulate a different UTM ==> interpreted languages (JAVA bytecode, e.g.)

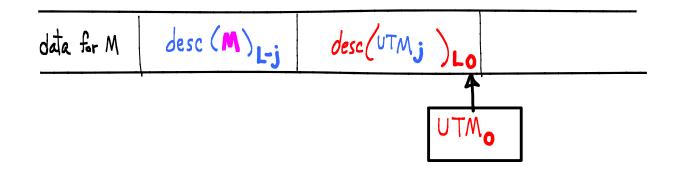

simulate desc-L0( UTM-j )

UTM-j has its own ISA, L-j.

Simulate UTM-j, which simulates M.

Let's make things even more exciting, add Heirarchy!

```

symbol "X" in L-Java,

===> symbol "X" in L-JVM,

===> desc-LC3( TM-X ) ===> executed directly, not via UTM-jvm simulation

OR

(hardware sub-routine)

```