What we are looking for

- -- A general design/organization

- -- Some concept of generality and completeness

- -- A completely abstract view of machines a definition a completely (?) general framework

- -- An introduction to a common, standard ISA

- -- An introduction to the LC3

Getting in tune with the current scene, listen to

Dave Patterson:

Computer Architecture is Back: Parallel Computing Landscape

http://www.youtube.com/watch?v=On-k-E5HpcQ

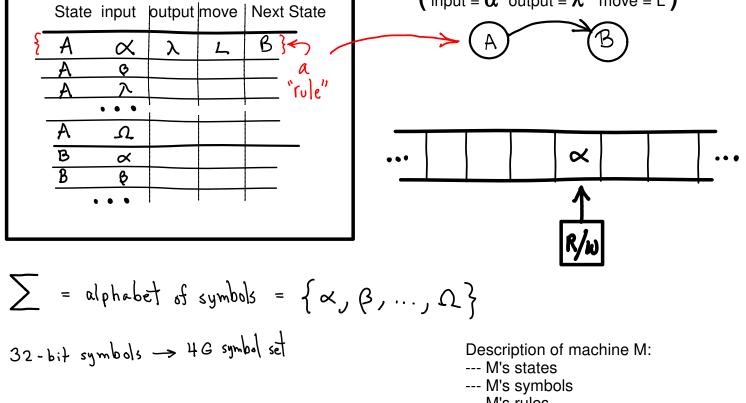

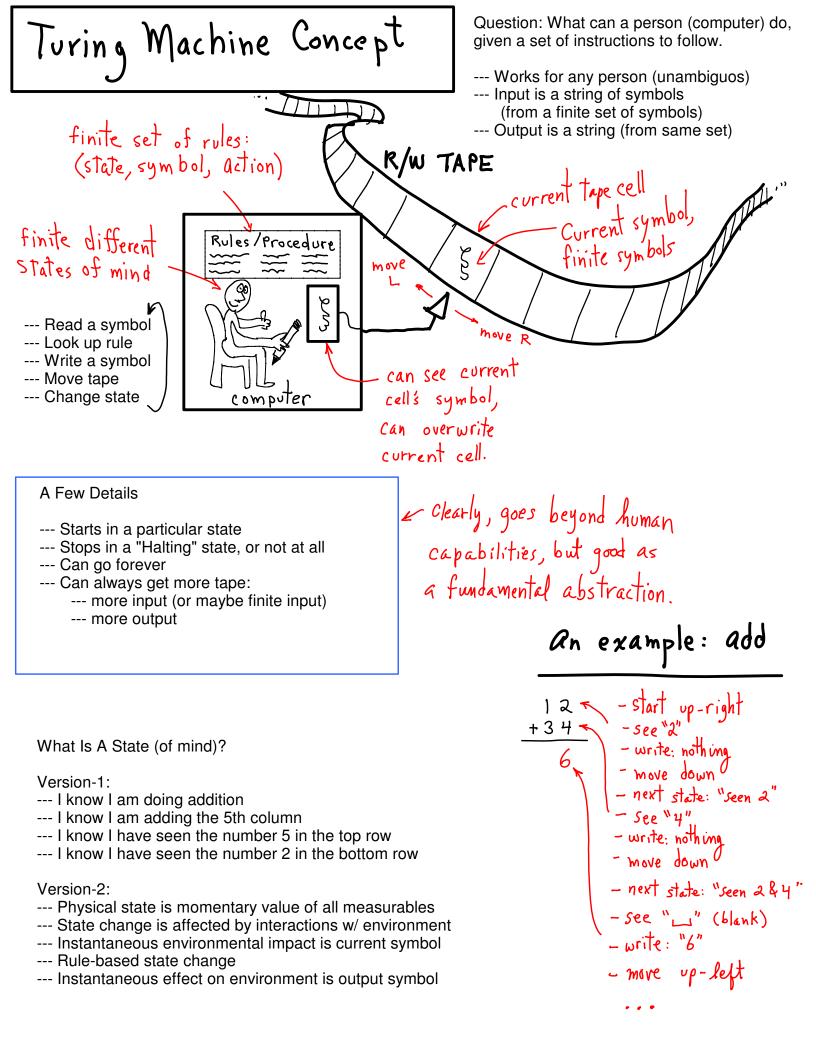

Completely General, Abstract Can prove mathematical statements Turing --- Define Algorithm Any computing machine (?) --- The UN-computable --- Define "Computation" --- Limits on Time/Space Machine Description a table of rules (input =  $\alpha$  output =  $\lambda$  move = L) State input putput move | Next State

--- M's rules

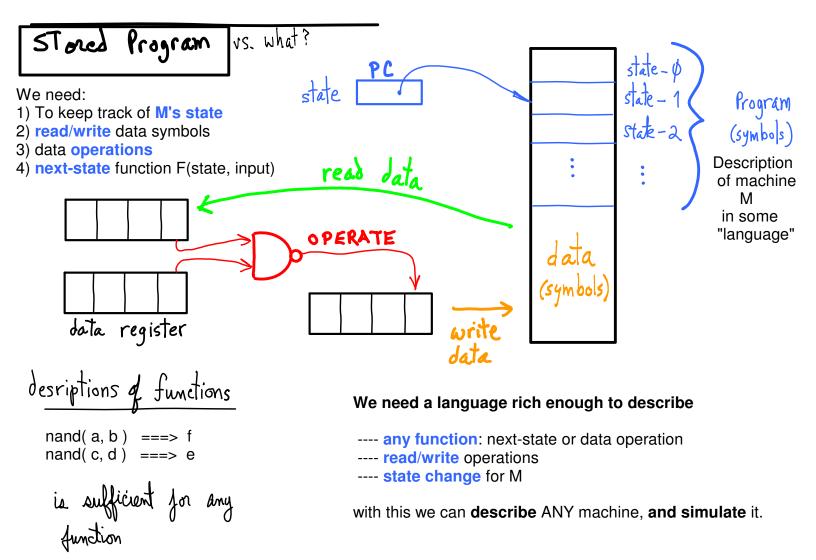

Program describes completely, how

- --- Machine M changes state

- --- next state depends on current state and current input

- --- output depends on input and M's current state

- --- M "moves" to another location to read next symbol

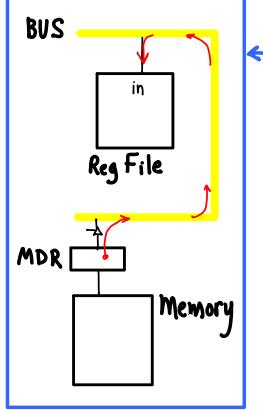

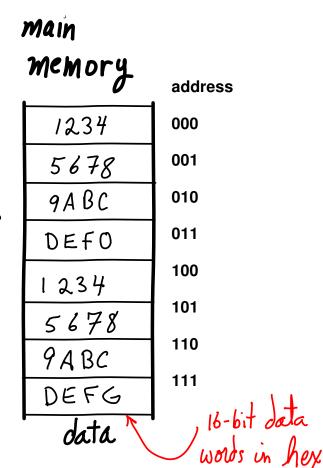

**Memory** == an array **address** == array index. Two Operations:

store data: in =

in ==> Memory[ address ]

retrieve data: out <== Memory[ address ]

and what else?

NB--It's not obvious what capabilities we need. Can we find a model that could tell us that?

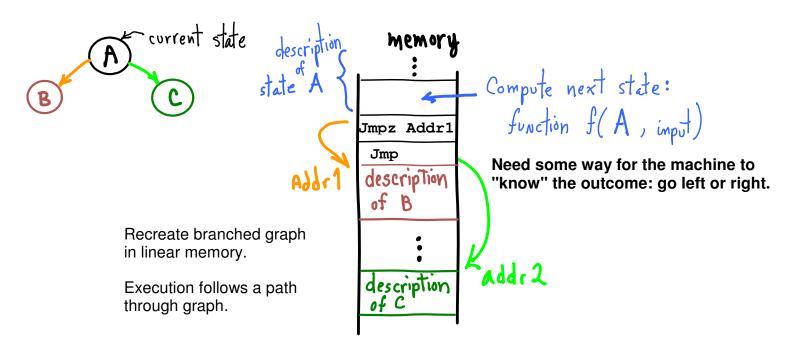

### Necessary for TM completeness:

--- Changing M's state

--- Go to other part of description (depending on data)

| address Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| data n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| data K out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| index/address content (symbols)<br>000<br>001<br>000<br>001<br>000<br>001<br>000<br>001<br>000<br>001<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000 |  |

memory

Content of Memory[00] is symbol p

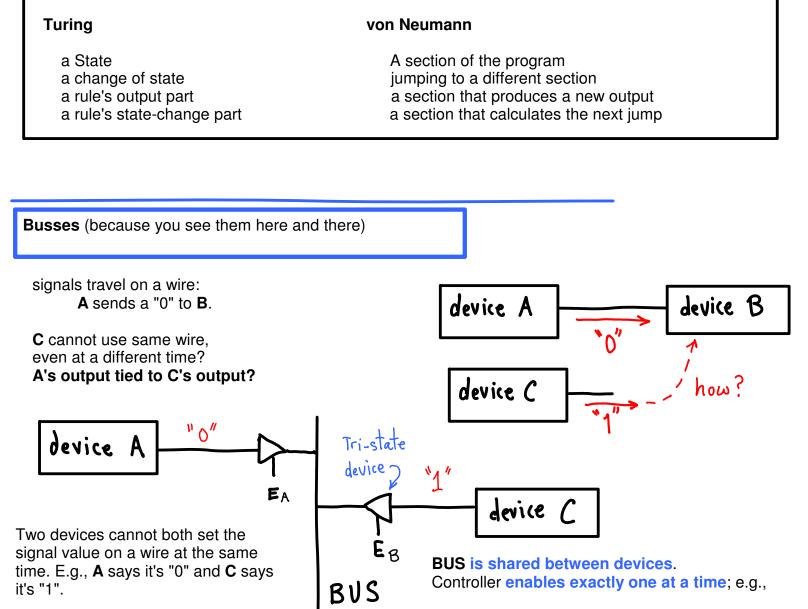

device B

E<sub>A</sub> ← `1″

$E_{B} \leftarrow 0''$

A is connected to BUS B is disconnected from BUS S

S

Verilog wire signal values

X -- unknown (for various reasons)

Z -- high impedance

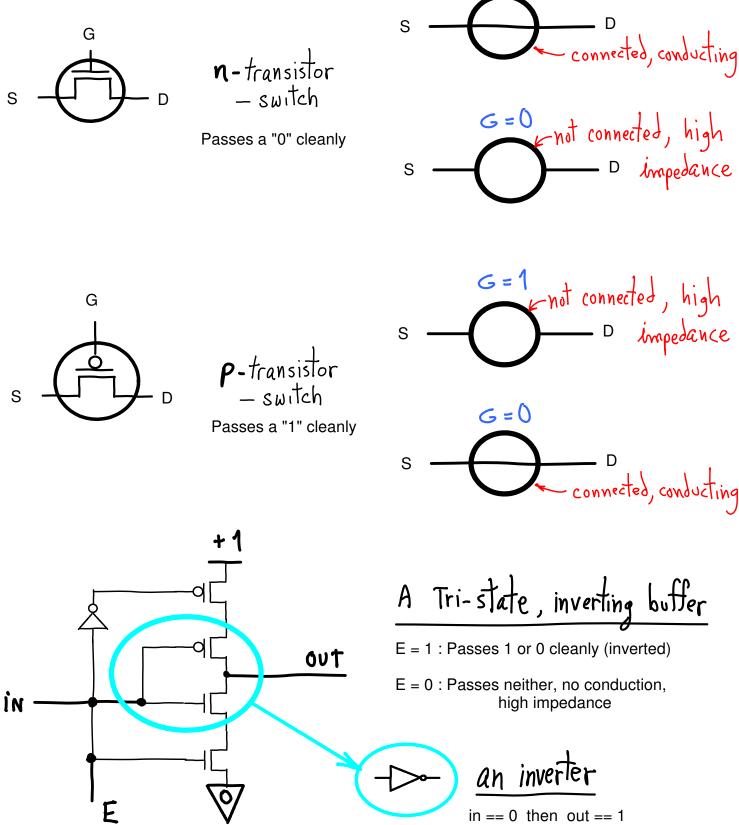

CMOS

1 -- voltage for "1"

0 -- voltage for "0"

in == 1 then out == 0

G = 1

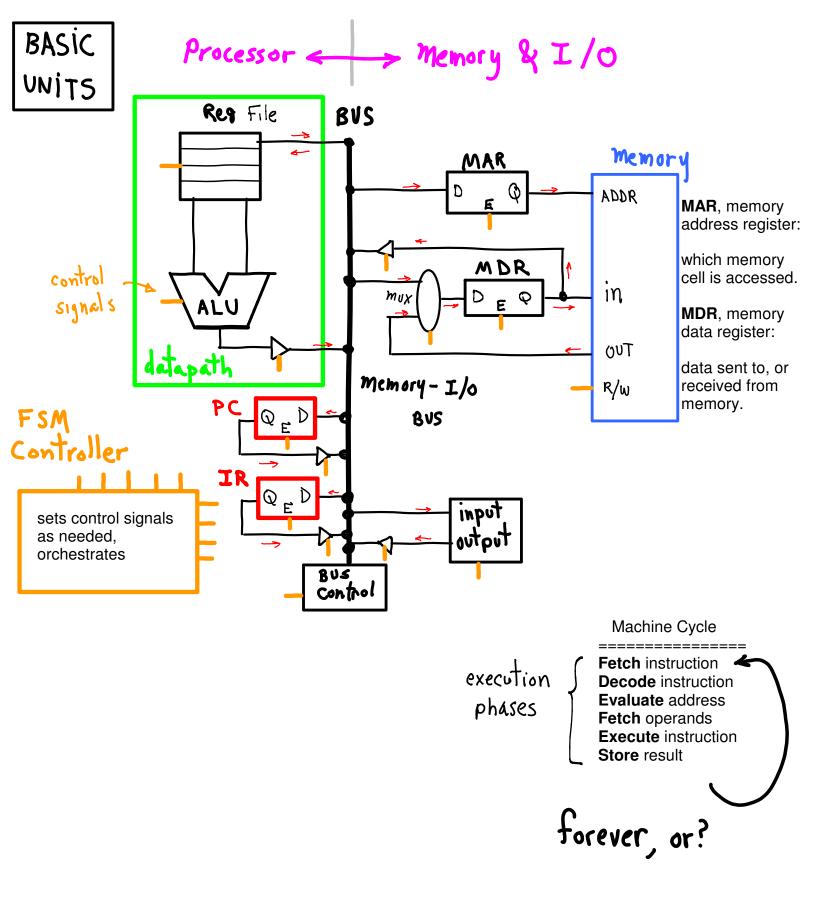

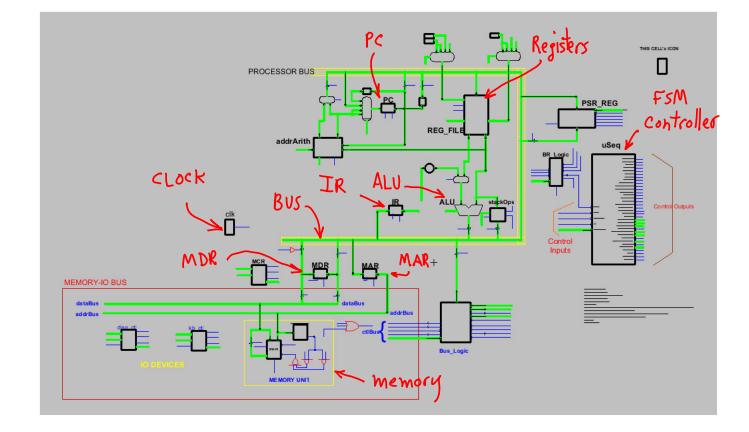

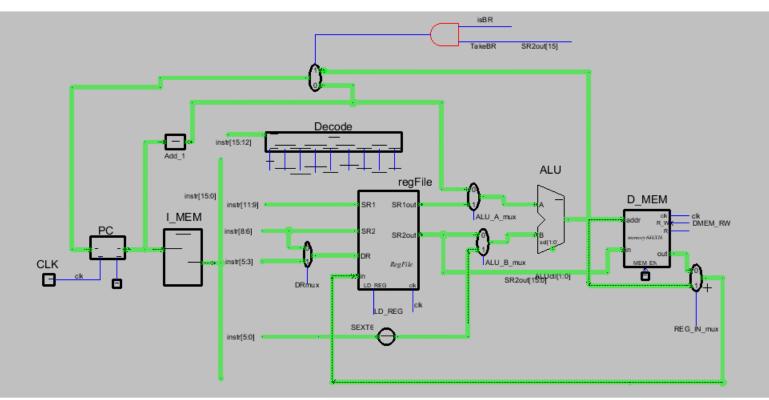

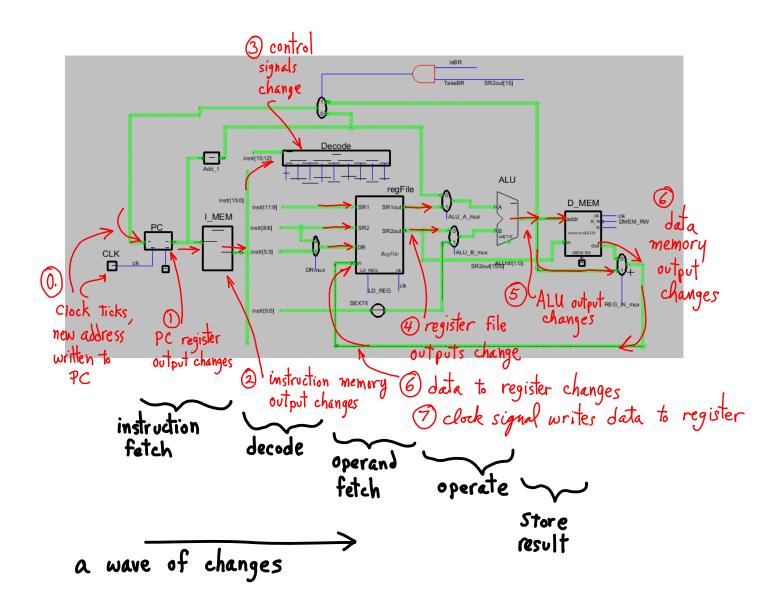

LC3, a von Neumann architecture

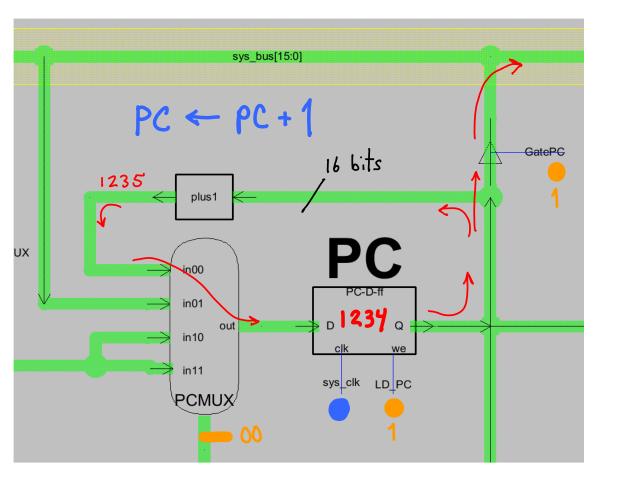

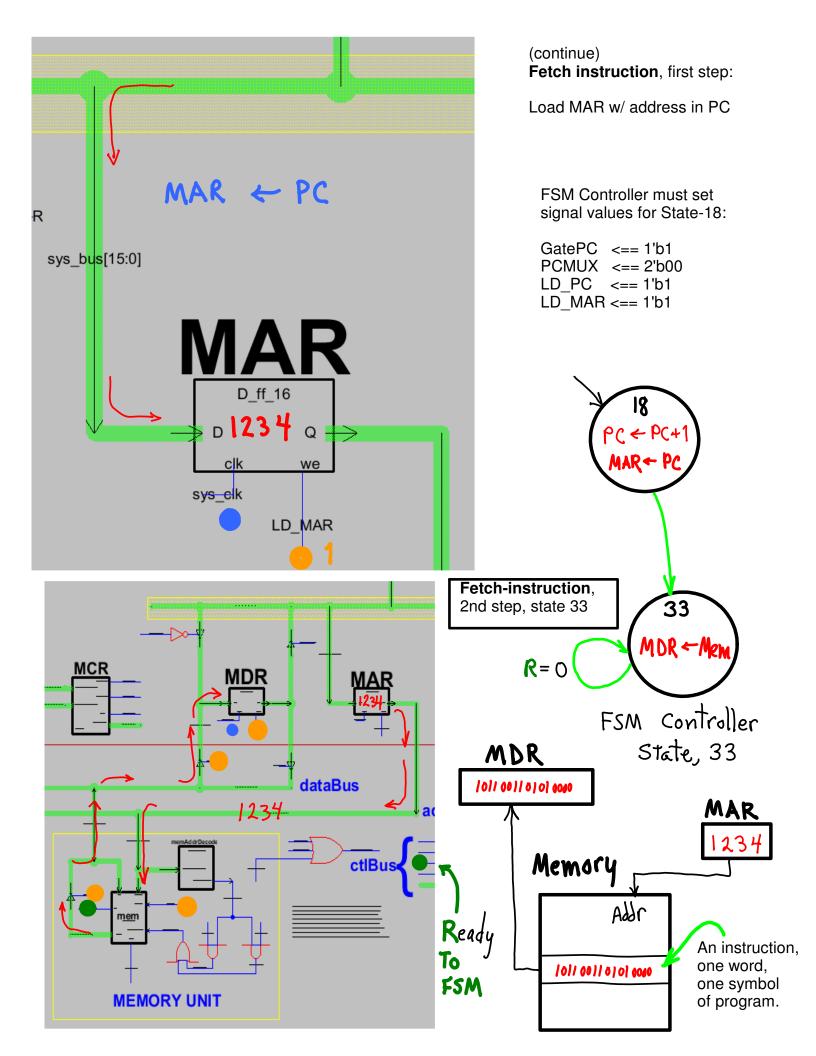

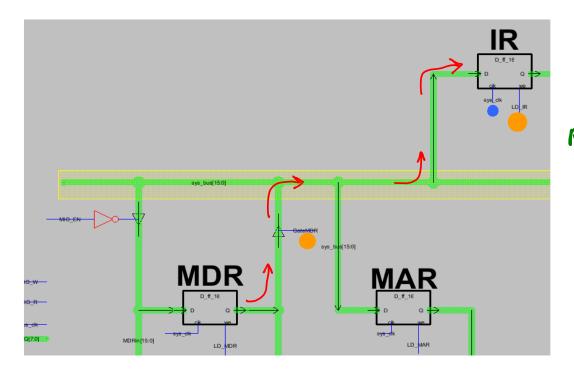

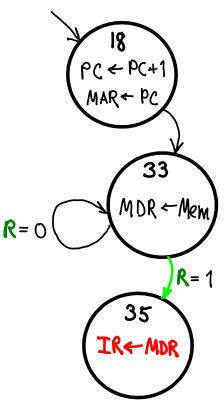

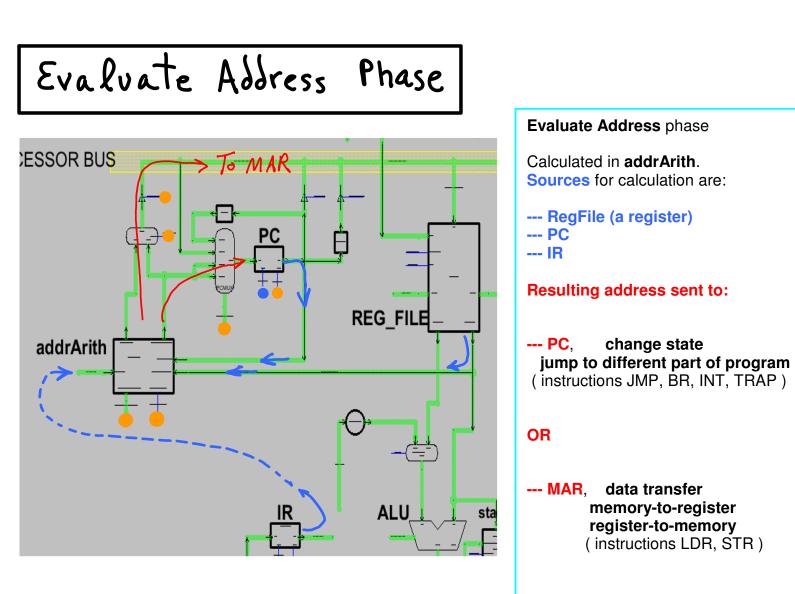

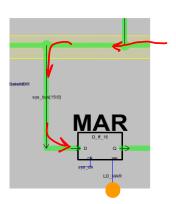

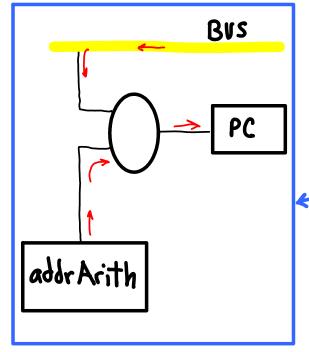

#### PHASE: Fetch instruction

-- 1st step, state 18

PC <== PC+1 MAR <== PC

(Happens in parallel, finalized when clock pulse arrives.)

# Continue to next state when $R \leftarrow 1$

This completes the **Fetch-instruction** phase.

#### **Overall effects:**

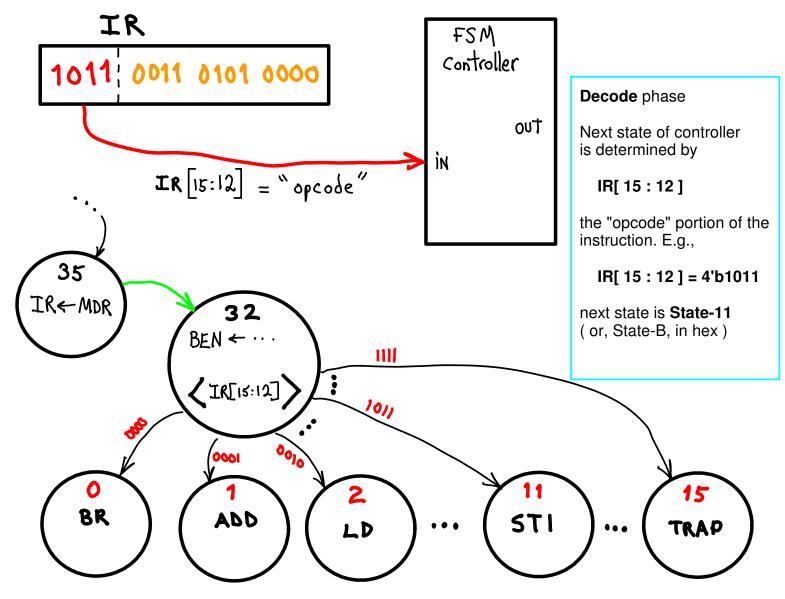

**IR** <== 16'b 1011 0011 0101 0000 (16-bit instruction, from memory)

**PC** <== 16'b 0001 0010 0011 0101 (a 16-bit memory address)

Or, to put it in other ways:

IR <== 16'h B350 IR <== Mem[ 16'h 1234 ] ) PC <== 16'h 1235

Fetch-instruction, 3rd step

Instruction is remembered, ie., "registered" in **IR**

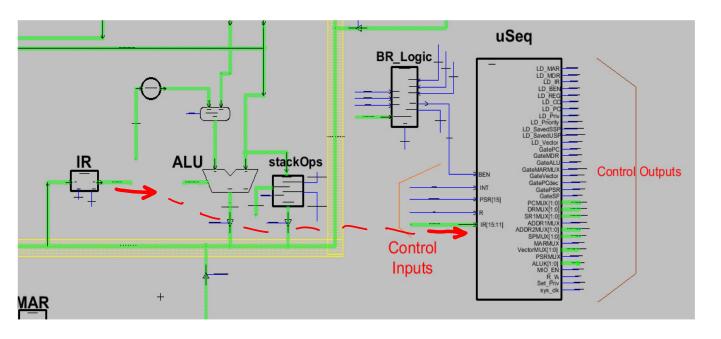

Control signals for state-35:

GateMDR <== 1'b1 LD\_IR <== 1'b1

# Decode phase, what instruction is this?

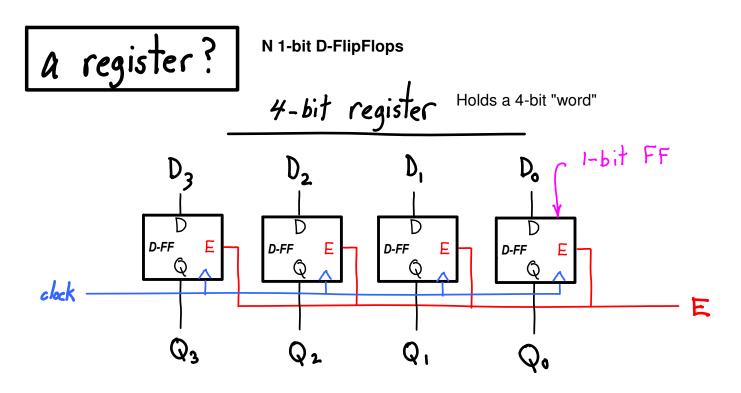

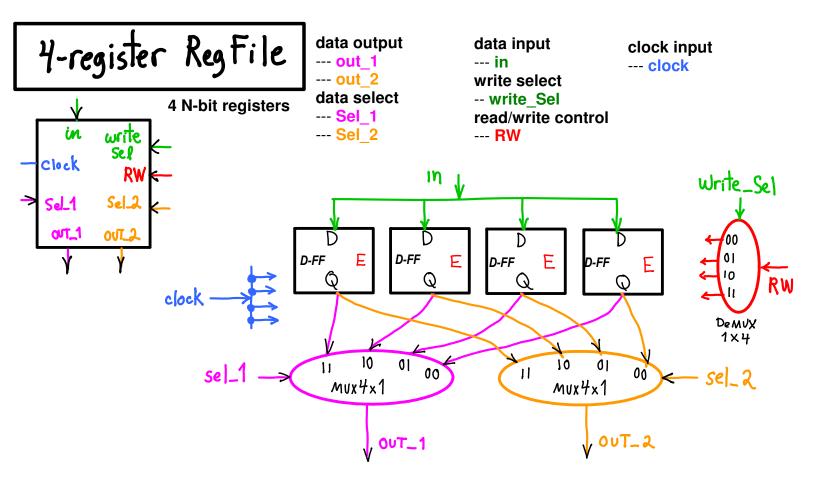

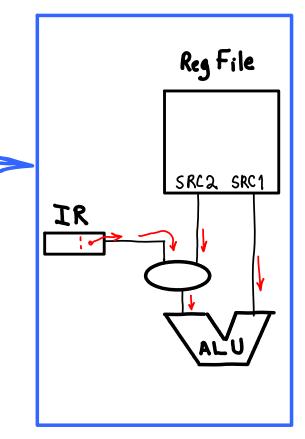

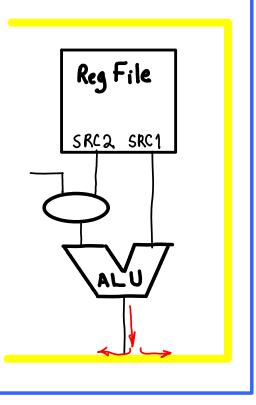

What's a Register File?

Some registers (flip-flops), and a way to select, --- which to output --- which to write

E=1: data D written to FF on next clock pulse

# Fetch Operands Phase

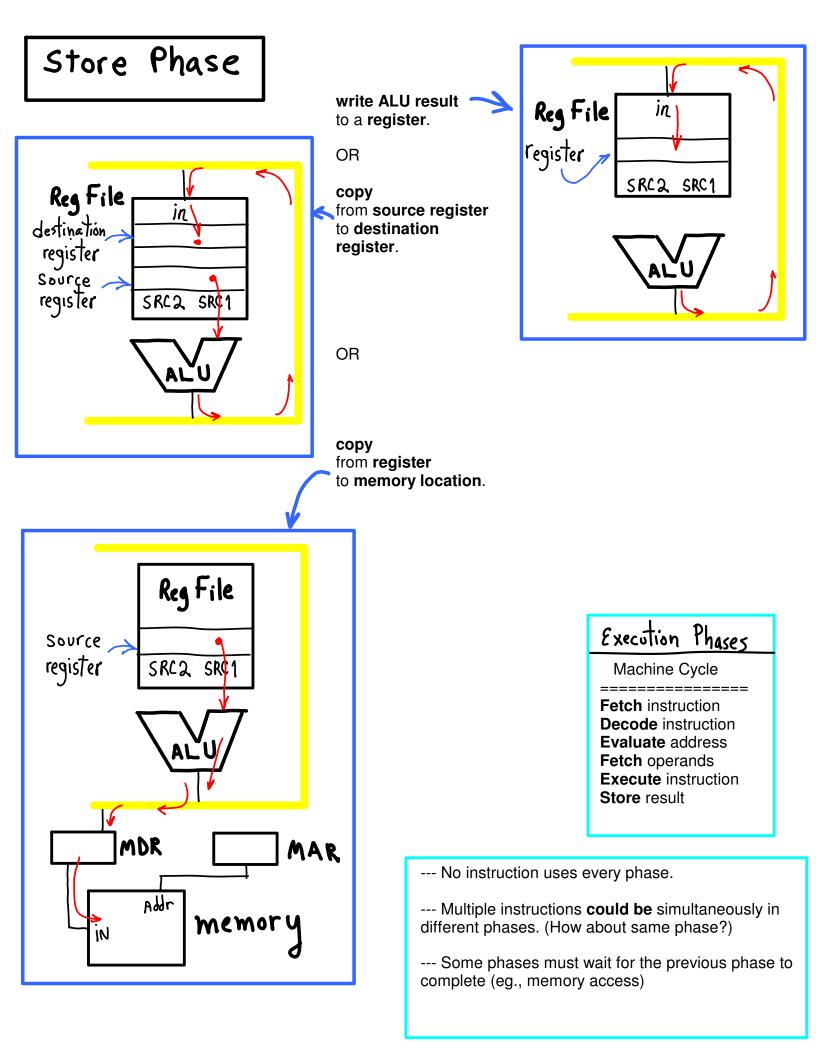

**move data from memory** to a **register** (e.g., LD)

OR

send data to ALU from a register or some of the IR's bits

LC3's "load from memory" instructions (LD, LDR, LDI) do nothing after copying from the **MDR** to a **register**.

ALU operation and making result available on BUS ( e.g., ADD, SUB, NOT)

### OR

Load the PC with an address calculated in Evaluate Address phase, or from another source (e.g., interrupt vector).

Instructions that do (2.) are **JMP**, **BR**, **TRAP**, as well as system generated action from hardware, **interrupts** and **exceptions**.

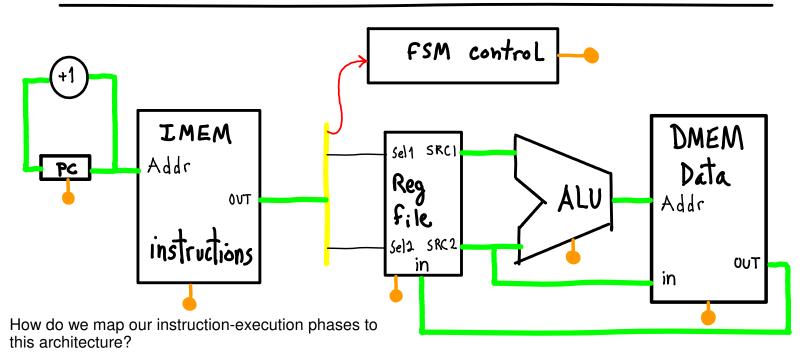

Harvard Architecture

Two memories, one for instructions, one for data. Layed out as a "pipeline" ==> more parallelism.

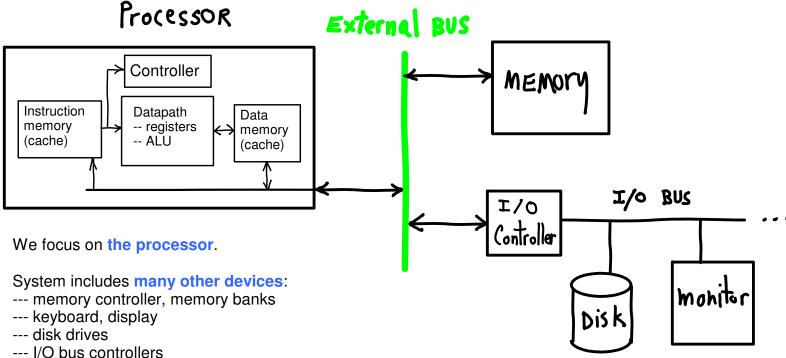

Processor

LC4, Harvard Architeture version of LC3

LC4, Only ONE cycle per instruction

- --- Two memories, instructions and data

- --- controller sets all control signals for proper flow

- --- Does not need IR, instruction memory output is stable

- vs.

LC3, many cycles per instruction

- --- One memory, used first for instruction, then data

- --- controller handles parts of operation at a time

- --- Needs IR to remember instruction

At large scale, system is von Neumann Architecture. At small scale, processor might be Harvard Architecture.

- --- network interfaces

- --- communication channels for video

- --- GPUs

- --- etc.

2 basic Architectures

- von Neumann - Harvard

Processors can be implement either way.

Systems are typically von Neumann.

Processors can be either von Neumann or Harvard (Intel x86, Pentium, ...).

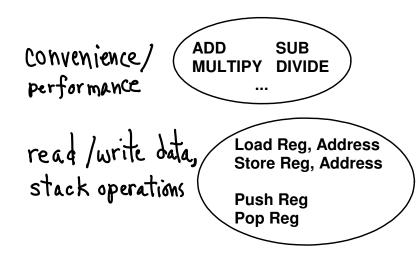

Enhancements (?)

- --- more processor hardware, built-in functionality (caches, branch prediction, ...)

- --- multiple processors

- --- simpler, low-power

- --- wider (more bits per register)

- --- wider (copied functional units)

- --- wider (multiple, different functional units)

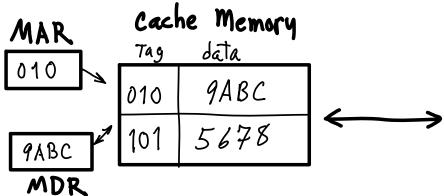

what's a cache?

A cache is a small memory.

**Cache Memory Read Operation**

```

Get address input.

```

```

cache "miss";

get data from Main Memory;

write tag+data into cell;

send data to output.

```

Writes are similar, but data goes the other way.

Data is transfered between cache and main memory as needed.

Cache is fast, main memory is slow.

Cache ABSTRACTION provides illusion that,

- ---- Access is just memory access: address goes in, data comes out.

- ---- Two Memories, IMEM and DMEM: separate, independent accesses

- ---- Single, unified, von Neumann memory: one memory, one address space.

#### Advantages

---- Memory access can appear to be very fast, when in fact it is very slow: If data is reused, cache can respond immediately, without waiting for slow main memory response.

---- Two caches allow two memory accesses in parallel (simultaneously).

#### **Cache Operation Complications**

Handling the new problems created:

#### ---- tag+data is not in cache?

Must **stall the processor** when cache misses? How do we stall a processor?

#### ---- write operation?

Will cache and main memory data differ? Should both be written at same time? Should we wait and write main memory later?

#### --- overlapping accesses from both caches?

IMEM reads instruction that DMEM is writing? Should IMEM wait until DMEM finishes? How would IMEM know DMEM is writing?

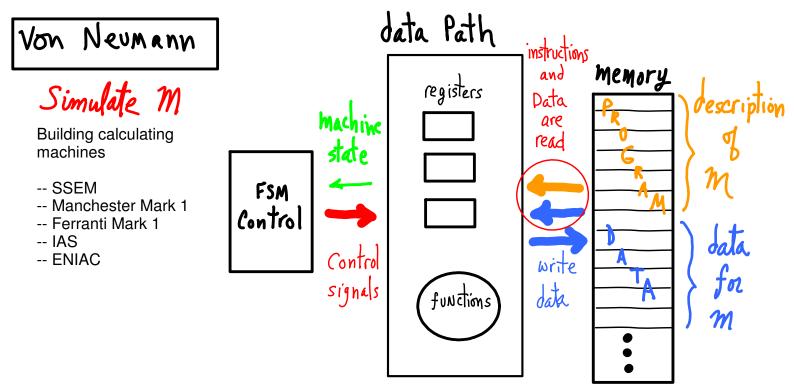

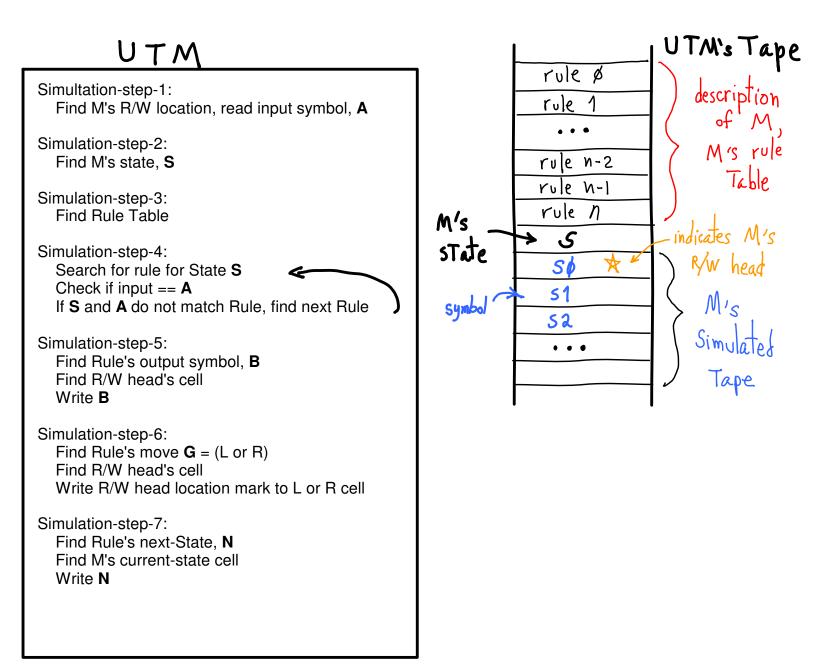

# Universal TM

A Turing Machine that Simulates other Turing Machines

Every computation can be modeled as some Turing Machine.

Doing computation X means building and running TM-x.

## Big idea: don't build new hardware,

### Build one simulator

For every other (new/special) machine, describe and simulate.

Build one simulator, and many descriptions.

--- describing == programming --- simulating == executing

### Language for describing TMs?

- --- The rule table describes a TM. Simple!

- --- Or, devise a programming language. More productive.

- --- Is the language Turing complete (can describe any TM)?

Eham: Computation is everywhere. Drah: Where? E: Everywhere! D: A car crash? E: Yes. D: A doll house? E: Yes. D: Me? E: Yes. D: What is the same about them? E: They all change. D: So, computation is change? E: Yes. D: Everything changes, so computation is everywhere?

- E: Yes.

- D: What is computation?

- E: Change.

D: So, everything changes, and because everything changes, everything is computation, and computation is change.

- E: Yes!

- D: Oh.

- E: You see, it is really quite simple.

- D: How simple?

- E: There is a model.

- D: A model?

- E: Yes.

- D: How is there a model?

- E: Things are one way, then they are another.

- D: And that means there is a model?

- E: Exactly.

- D: How do I know there is a model?

- E: That is an existence proof.

- D: What is?

- E: I just said there is a model, didn't I?

D: And a model means things are one way, then another.

E: Now you've got it.

- D: Isn't that the same as change?

- E: Quite right.

D: So, a model is change and change is computation and change is computation because there is a model?

E: See, now you're getting the hang of it. D: Oh.

- D: So, what is a computer?

- E: Something that does computation.

- D: Doing computation?

- E: That's it, computing.

- D: So, computers compute?

- E: Obviously.

- D: And computing is change?

- E: What else could it be?

- D: Everything changes, so everything is a computer?

- E: Yes, absolutely.

E: Without a doubt. When you change, which you do constantly, you are computation.

D: Then, I'm not me before, nor me after, but I'm me as I change?

E: Computation is everything and everywhere, all things are changing, you are changing, you are computation.

- D: What if I don't change?

- E: Everything changes.

- D: So, there is nothing that doesn't change?

- E: That's right, nothing doesn't change.

- D: So nothing isn't computation. Does nothing exist?

- E: Of course nothing exists. There is zero, zero exists.

D: So 0 is not computation?

E: That's right, because 0 is nothing. If it were something, then it would be computation, because all things change. D: So, does 1 exist.

- E: As surely as anything exists, as certainly as zero exists.

- D: But they don't change, 0 and 1, I mean?

E: Of course not.

- D: Then something exists which is not computation?

- E: Absolutely.

D: But, if computation is everywhere, where are 0 and 1?

- E: Right there.

- D: Where? On the ceiling?

E: Of course. See that thing there? There is only 1 of them there.

- D: So that's the existence of 1?

- E: What could be clearer?