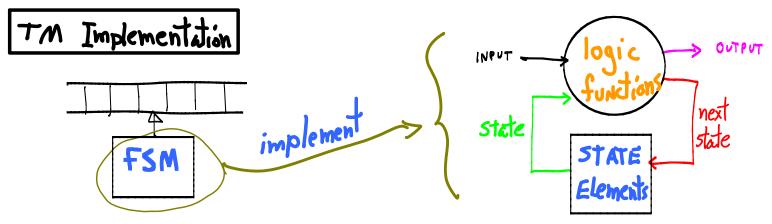

To build any TM, WE NEED:

- ---- (1.) FSM: state logic functions (output and next-state)

- --- (2.) Tape: methods to R/W symbols, we'll use registers (RAM).

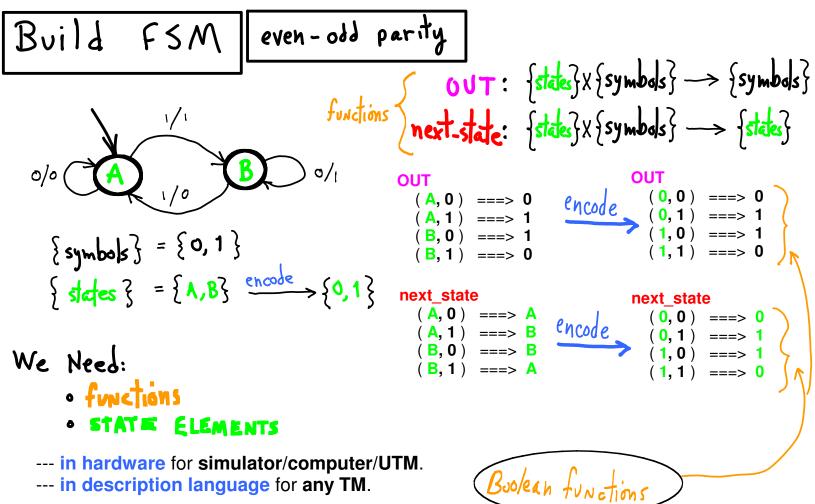

--- (3.) Symbol set = a set of fixed length bit strings, e.g.,  $S = \{0,1\}$ (2 symbols)  $S = \{00, 01, 10, 11\}$ (4 symbols)  $S = \{000, 001, 010, 011, 100, 101, 110, 111\}$ (8 symbols)

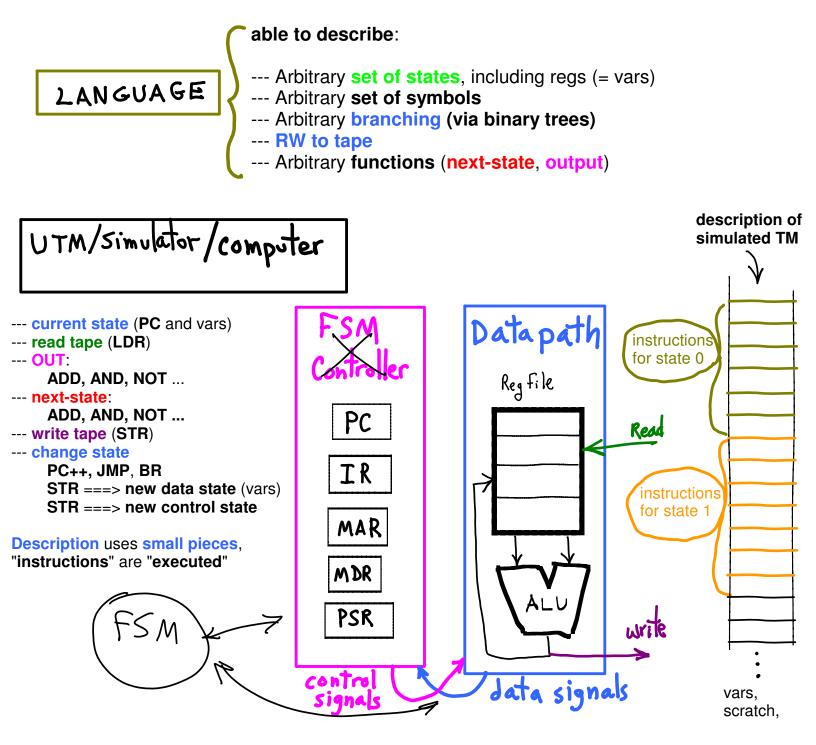

---- in description language for any TM.

**Universal** (able to **simulate any TM**)

- --- language to describe any TM,

- --- Simulator that understands that language.

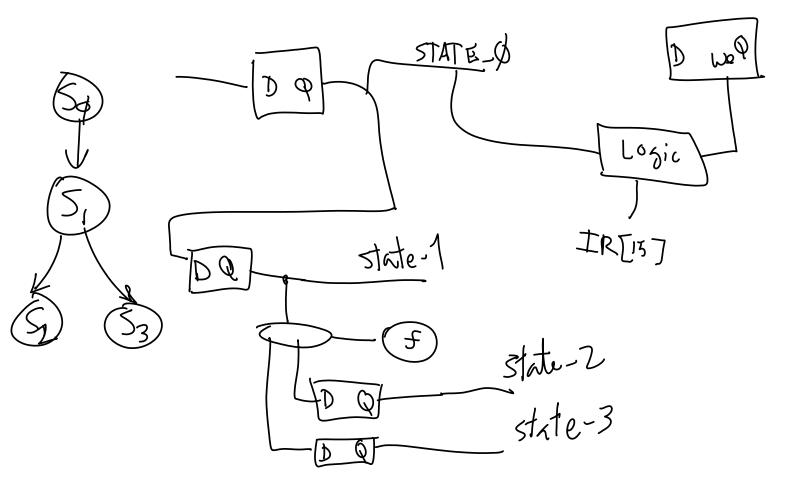

FSM Controller uses registers (e.g., PC) to remember:

- --- simulated machine's state (control + data states)

- --- simulated **symbols read** (RegFile)

- --- simulated write symbols (RegFile)

- --- step of simulation (UTM's controller's state)

- --- partial steps of function evaluations (next-state, output) data registers, PSR, on tape, ...

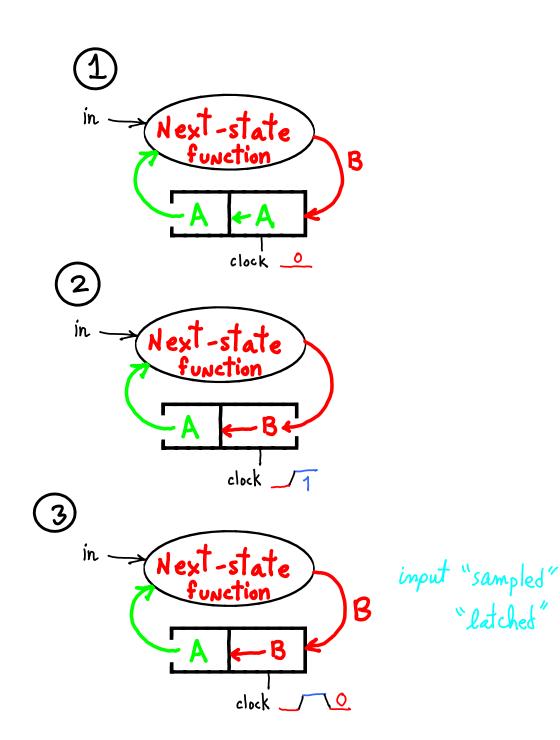

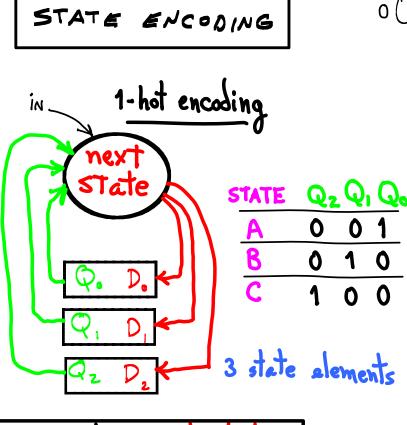

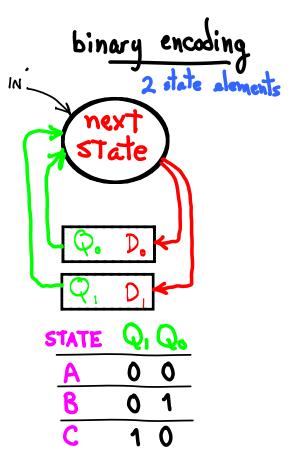

STATE ELEMENTS pos. edge-triggered FF

Feedback loop: state change, NS change, state change, NS change, ...

Advantages of "random logic" controller:

- -- faster

- -- smaller (?)

- -- distributed throughout machine

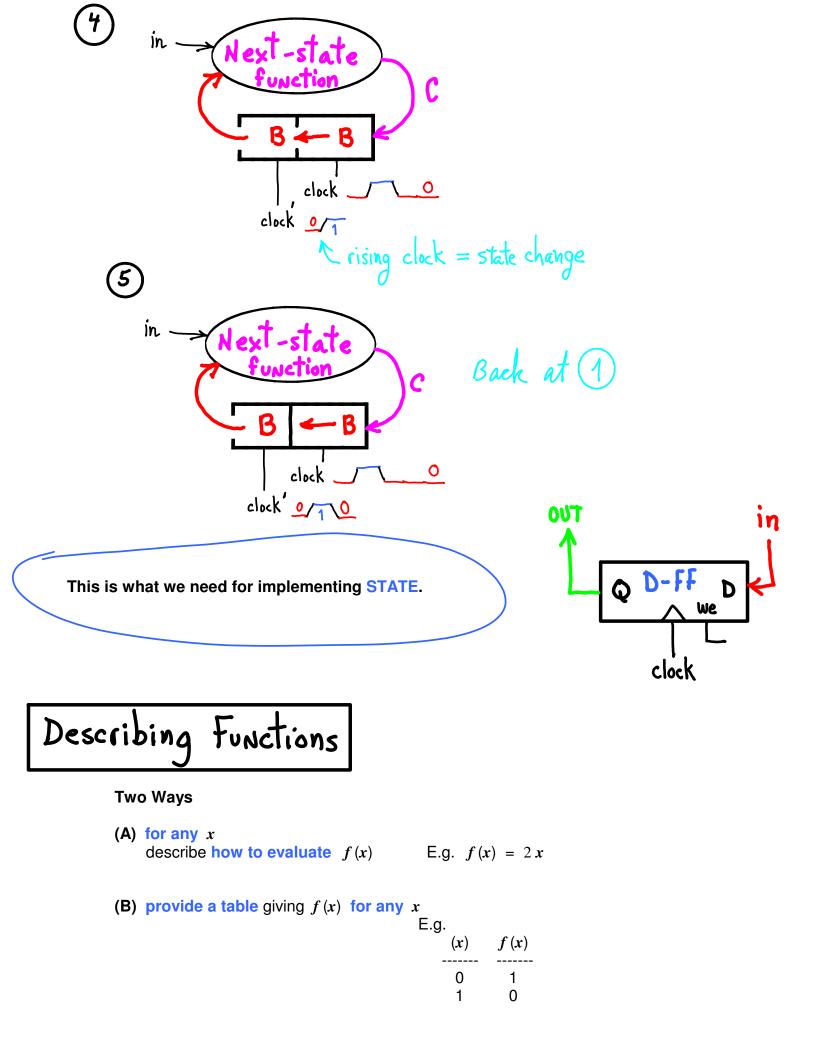

Caveat: The C-Reg is just to make the picture clearer, it doesn't actually exist in LC3.

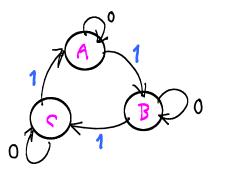

WE HAVE (suppose for now)

- --- 1-bit state elements

- --- 1-bit function elements

HOW to put them together?

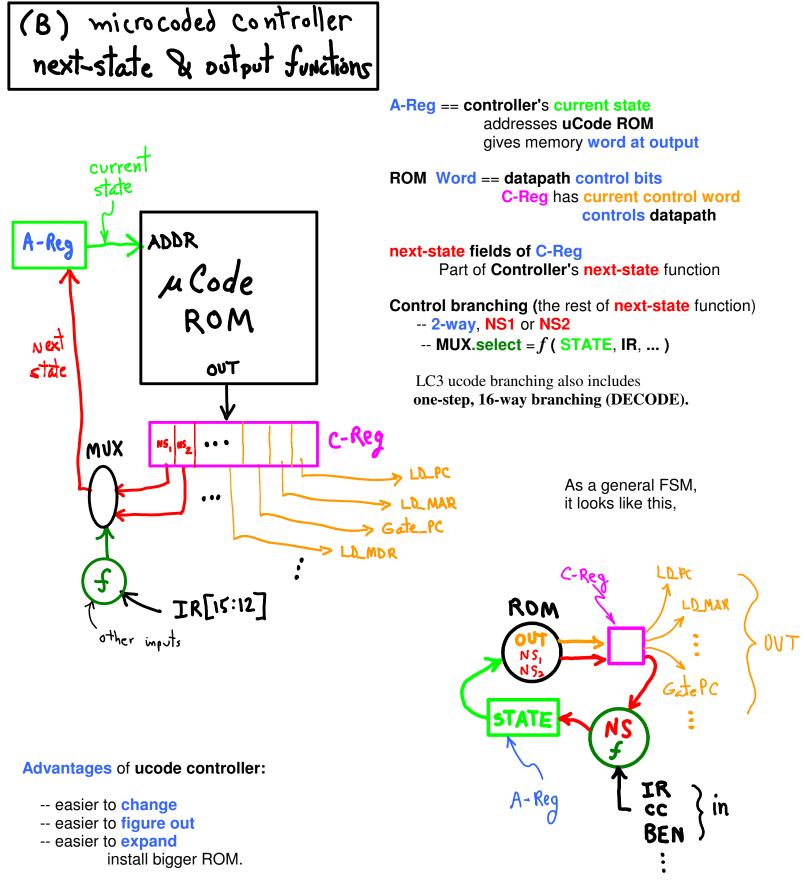

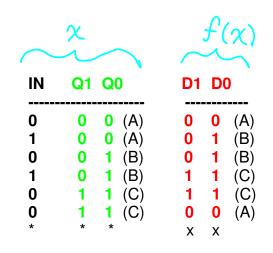

A mod-3 machine

| Describe | next-state |  |  |  |  |  |

|----------|------------|--|--|--|--|--|

| function |            |  |  |  |  |  |

| IN | Q2 Q1 Q0 |   |              | D2 D1 D0 |   |   |     |

|----|----------|---|--------------|----------|---|---|-----|

| 0  | 0        | 0 | 1 (A)        | 0        | 0 | 1 | (A) |

| 1  | 0        |   | 1 (A)        | 0        | 1 | 0 | • • |

| 0  | 0        | 1 | 0 (B)        | 0        | 1 | 0 | (B) |

| 1  | 0        | 1 | <b>0</b> (B) | 1        | 0 | 0 | (C) |

| 0  | 1        | 0 | <b>0</b> (C) | 1        | 0 | 0 | (C) |

| 1  | 1        | 0 | <b>0</b> (C) | 0        | 0 | 1 |     |

| *  | *        | * | *            | х        | х | х |     |

\* rows not shown, don't matter? X is for **don't care**, either 0 or 1.

\* rows cannot be reached.

IF we have a universal language (able to describe any TM)

All we need to know is **How To Build**:

- --- 1-bit state elements?

- --- 1-bit functions?