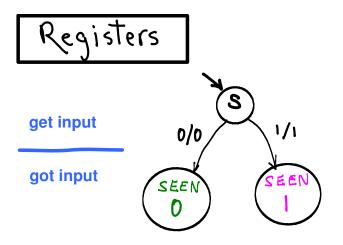

"SEEN 0" registers that we've seen a 0.

"SEEN 1" registers that we've seen a 1.

State "registers" or "remembers" what we have seen.

TM's FSM (the CONTROL part of a TM)

No tape

one input two outputs IN OUT, MOVE

inputs/outputs are time series:

time: 0 1 2 3 4 5 6...

IN : 0 0 0 1 1 1 0 ...

OUT : 0 1 1 0 1 0 1 ...

MOVE: 0 1 1 0 1 0 1 ...

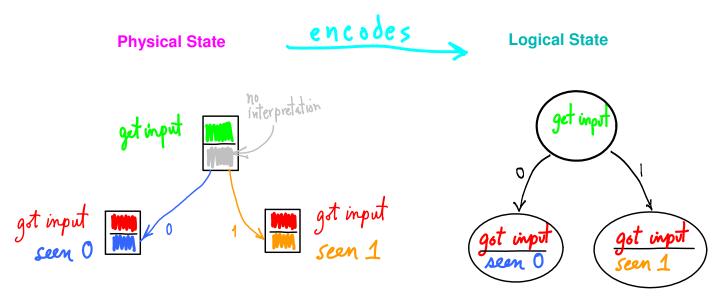

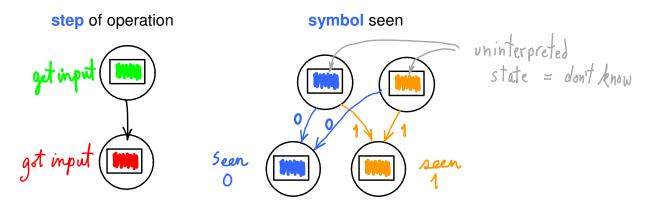

Physical state changes in time.

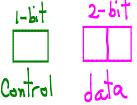

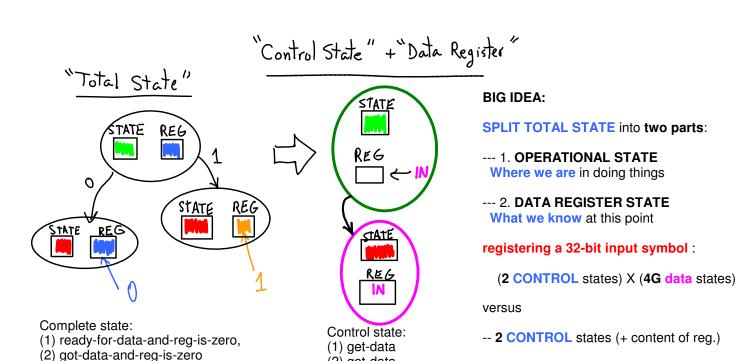

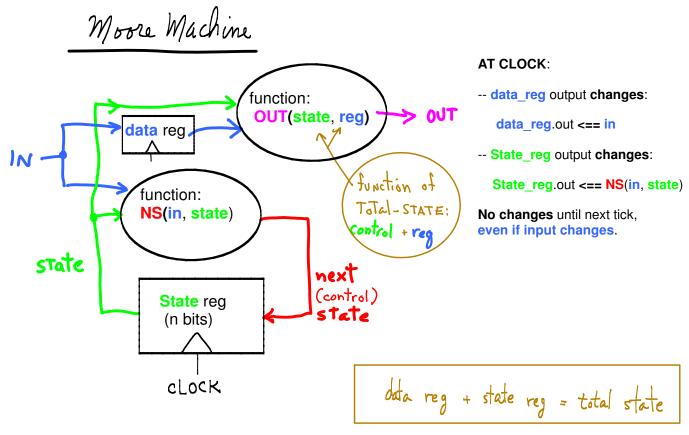

STATE can be thought of as consisting of **two parts**:

physical device

1-bit Reg

2 possible states

Can register one of two data

2-bit Reg

4 possible physical states

1-bit register  $==> 2^1 == 2$  states

**k**-bit register ==> 2^**k** states

2 1-bit registers ==>  $(2^1)(2^1)$  == 4 states 2 **k**-bit registers ==>  $(2^k)(2^k)$  ==  $2^k(k+k)$  states

Physical system, 8 states:

| control |   | data |

|---------|---|------|

|         | 0 | 00   |

| ١       | 0 | 01   |

| ₹.      | 0 | 10   |

| ι       | 0 | 11   |

| ,       | 1 | 00   |

| ١       | 1 | 01   |

| ₹       | 1 | 10   |

| ı       | 1 | 11   |

| •       |   |      |

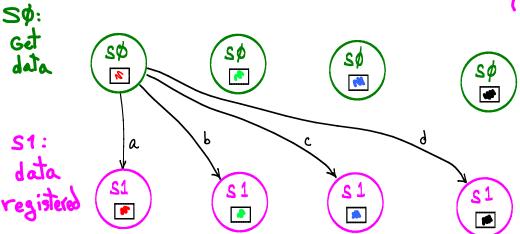

Before reading input ( "get-data" control state): we don't care which of upper 4 states we are in.

After reading, ("data-registered" control state) we are in one of 4 states, data is recorded.

32-bit data ==> 4G branches. We'd like to ignore data state, concentrate on control state.)

(2) got-data

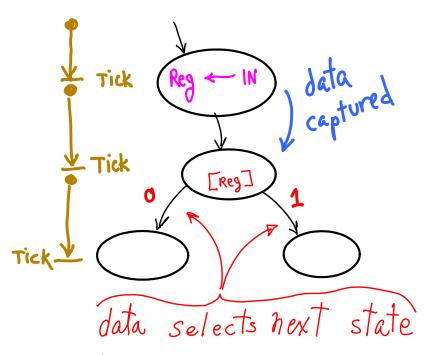

### Control Branching

(3) got-data-and-reg-is-one

Next CONTROL state depends on register content.

- -- States === Register Transfers

- -- Branches labeled w/ register content.

#### **CLOCK** causes:

- ---- register transfers

- ---- control state changes

#### **REGISTERS** for

- ---- CONTROL STATE

- ---- DATA

- ---- BOTH types change w/ CLOCK

We choose which part of data state is relevant, ignoring the rest.

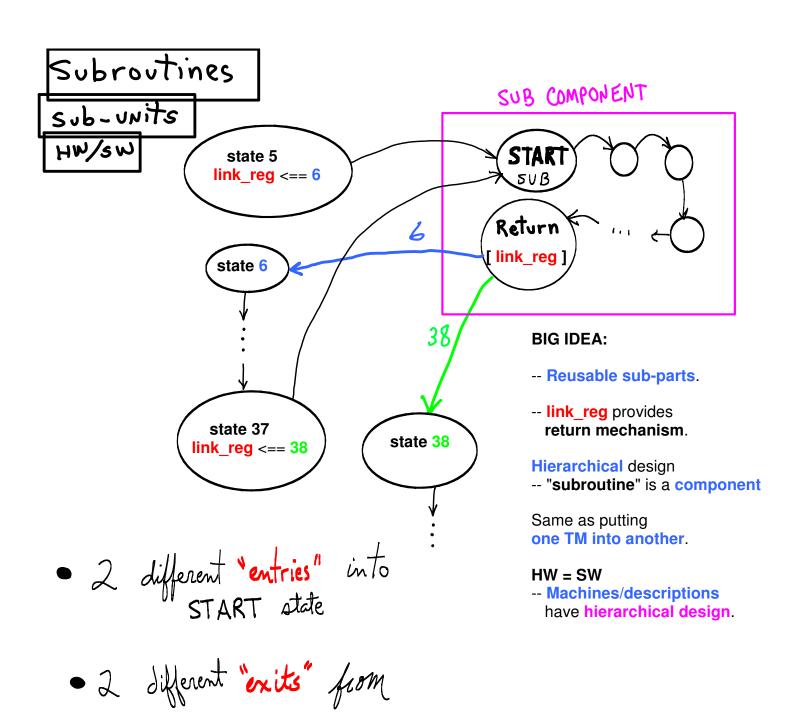

Reusable Sub-"Routine"

HALT state

## Implementation of FSM

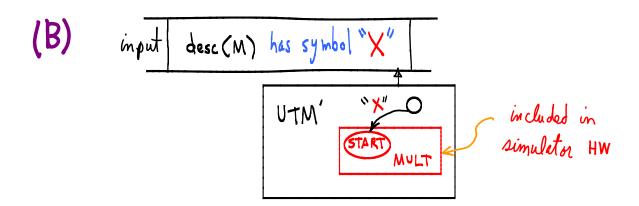

BIG IDEA: Extend simulator with additional hardware (hardware subroutines).

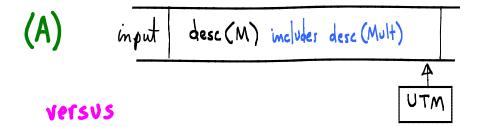

- --- (A) simulated M's description has sub-routine, desc( MULTIPLY )

- --- versus (B) add a symbol "X" to M's description

branch to a hardware MULTIPLY subroutine:

===> New Simulator is FASTER,

===> Desc(M) is SMALLER: desc( MULTIPLY ) is gone

--- Software == Hardware

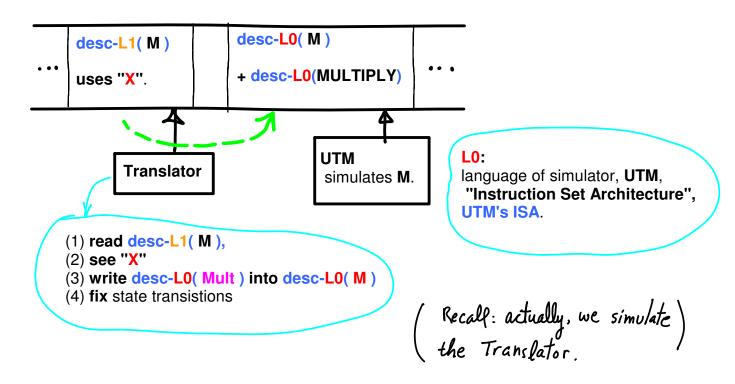

# Hierarchical Translation variant of (A)

Could we extend desc(M) in the same way?

"X" in desc( M )

Translator adds desc(MULTIPY) to desc(M)?

===> **Libraries**, code inserted where referenced.

--- Add layers of translation

- --- Migrate subroutines down (maybe into UTM's hardware)

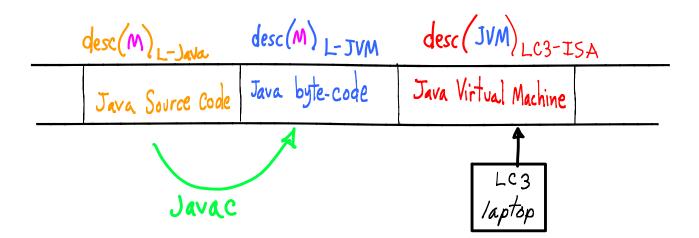

- --- Simulate a different UTM ==> interpreted languages (JAVA bytecode, e.g.) simulate desc-L0( UTM-j )

UTM-j has its own ISA, L-j.

### Simulate UTM-j, which simulates M.

Let's make things even more exciting, add Heirarchy!

```

symbol "X" in L-Java,

===> symbol "X" in L-JVM,

===> desc-LC3( TM-X ) ===> executed directly, not via UTM-jvm simulation

OR

(hardware sub-routine)

```