## NAME

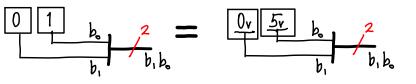

At right is an FSM, M, implemented as a ROM and two flipflops. M has no outputs. ROM words are two bits, each implemented as a connection to voltage source (0v or 5v). E.g., shown below is a word whose logical content is 01.

Bits are connected low-bit to low-bit, and so on in order. E.g., For any ROM word [ b1b0 ],  $b_0$ connects to **D**0: bı connects to D1. Also.

- *input* connects to A<sub>0</sub>;

- $\mathbf{Q}_0$ connects to A1;

- $O_1$ connects to A2.

Addresses are connected so that, e.g.,

10 10

00

11

0

*in*-110 has address A[2]A[1]A[0] = 110Thus, A[0] = 0, is the low address bit and is coming from the *input* = 0.

**Q.** How many different FSMs could be implemented using this hardware? That is, suppose a designer makes a table of the ROM's content for an implementer (an 8-row table of two-bit words), who then connects each memory bit to its proper voltage. How many different tables is it possible for the designer to come up with for this ROM? Would each such table implement necessarily a different machine?

There are 16 bits in the ROM, and each can be 0 or 1. So, there are  $2^{16} = 2^{6} \cdot 2^{10} = 64 \text{ k}$  different possible tables. Each defines a unique machine. 00 10 Q. Implement such a table for the FSM, M, shown at right. That is, fill in the logical content (using 0 and 1) of the ROM above so that it implements M. Each state is labeled with its state encoding. STATE 01 11 00 0 0 10 01 1 00

ROM 0 0 in-000 in-001 in-010 in-011 b, b oil in-100 in-101 in-110 in-111 input, 1 A. address Q. Q,Q D,D. Q

Shown at right is an expansion of the hardware above to provide for implementation of general FSMs. It adds a mechanism for output.

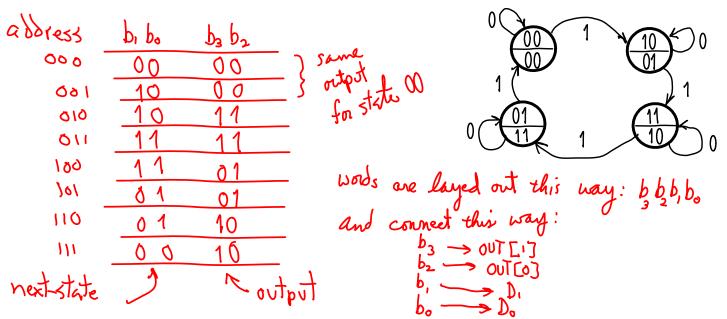

**Q.** We now need two 8-row tables to specify a particular FSM. Suppose the designer wanted to combine the tables into one 8-row table. How would the ROM be redesigned to accommodate this? How many bits would be needed for each ROM word? Show the assignment of the bits of a typical ROM word to each of OUT[1], OUT[0], D[1], and D[0].

Each word has 4 bits  $\begin{bmatrix} b_3 b_2 & b_0 \\ b_1 & D_0 & b_2 \\ b_1 & D_1 & b_3 & OUT_1 \end{bmatrix}$

for t. FSM. o one 8modate rd? o each input 1 statk ROM out 3 hextstatk ROM hexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthexthex

**Q.** At right is a Moore FSM (output depends only on state). Give a single table for its implementation ROM.

**Q.** How could the table above be recoded into a linear form suitable for simulation by a Universal Turing Machine? (Assume bit b<sub>0</sub> of M's output is used to implement moving its R/W head left or right, and bit b<sub>1</sub> is its output symbol. At the clock tick, the R/W head moves and state changes.)

Each Row would be coded < current-state, input, output, more, next-state) These fields come from ROM, encodes in unary. Remaining fields are encoded address bits.