## final exam

COSC-120, Computer Hardware Fundamentals, fall 2012 Computer Science Department Georgetown University

NAME \_\_\_\_\_

Open books, open notes (laptops included). **Answers w/o explanation get 0 credit**. Credit is based on **your explanation, not correctness**. Show and explain **all** your work from first thoughts to final answer.

MAR <--PC

MDR<-M

IR<-MDR

BEN<-IR[11] & N + IR[10] & Z + IR[9] & P

[IR[15:12]]

Π,

To 49 (See Figure C.7)

To 13

## I.

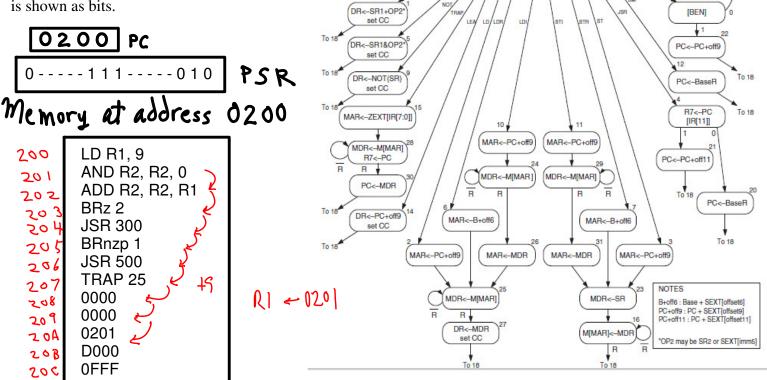

At right is part of the LC3 controller's statetransition diagram. The parts missing handle interrupts (state 49), and exceptions (states 8 and 13). The questions that follow assume the controller has just entered state 18. Shown below are the relevant portions of the LC3's state. Register values and addresses are shown in hex, except for the PSR, which is shown as bits.

To 8

(See Figure C.7)

AND

Memory content is translated into LC3 assembly language, except that offsets are shown as hex values instead of labels. Data words are also shown as hex values.

**Q.** Which instructions change the PSR content, according to the state-transition diagram?

In the diagram, "set CC" indicates a state that changes the CC in the PSR (states ", 5, 9, 14, 27). The PSR content also includes Privilege (PSR[15]) and Priority (PSR[10:8]), but states that change these are not shown here. **Q**. A clock cycle is 1 ns. Accessing memory takes 10 clock cycles; e.g., the controller remains in state 33 transitioning on the "R=0" arc 10 times before transitioning on the "R=1" arc to state 35. How long does it take to complete an instruction fetch? That is, given we have just transitioned to state 18, how long before we transition to state 32?

Ins/state change + 10 ns in state 33 → 13 ns elapse until we enter state 32.

Q. How many clock cycles before the PC first contains a value greater than 02FF?

This address is not local: it must be a non-local jump. That is either JSR 300 or JSR 500, or TRAP. JSR 300:  $PC \leftarrow 205+300$ . The BR3 is not taken because ADD R2, R2, R1 is not 300: LD(13+14) ns, AND(13+2)ns, ADD(13+2)ns, BR3 (13+2)ns, JSR(13+3)ns = 5(13) + (14+2+2+2+3) = 65+23 = 81 cycles

**Q**. How many words of memory are represented above by the program and its data? This includes every word of the memory content shown. How many bits, in total?

Every instruction is one word -> 8 words for instructions. Data is 5 words -> 13 words (16 bit) = 13×16 bits

**Q**. Assume memory address 0025 contains 0200. Will the program above ever make a jump outside of the range 0200 to 1000? That is, is there any instruction shown above that will change the PC to have a value less than 0200 or greater than 1000? If so, which instruction?

The BR3 is local, JSRs jump to ~ (200 + 300) m (200 + 500) < 800. Timps to 0200 because vector at 0025 à 0200, so ho j'umps are jurther than +1000, and no jumps jo below 200.

**Q**. Trace out the program's execution instruction-by-instruction: Just after completing an instruction's execution (just after the LC3 next enters state 18), show (1) the CC bits, (2, 3) the number of states entered and the number of ns elapsed since last entering state 18. Stop tracing when the PC first contains 0208.

| instr, executed | NZP | # states | # ns    |                               | instr, executed | NZP | # states | # ns          |

|-----------------|-----|----------|---------|-------------------------------|-----------------|-----|----------|---------------|

| LD              | 001 | 7        | 7+10+10 |                               | JSR 300         | 001 | 5        | 5+10          |

| АИЛ             | 010 | 5        | 5 +10   | not sure these                | BRNJP           | ??? | 6        | 6+10          |

| ADD             | 00  | 5        | 5410    |                               | TRAP            | ??? | 1        | 1 PC 4 PC+1   |

| BRZ             | 001 | 5        | 5+10    | set executes<br>because not   |                 |     |          | ( is state 18 |

| v               | •   | •        | I       | Aure JSR 300<br>returns. also | don't know      | NZP | fter J.  | ¥ = 208       |

Q. Suppose again that the memory location at address 0025 contains 0200. Also assume the instructions at addresses (200+5+300 and 0200+7+500 are JMP R7. Will this program enter an infinite loop? 6005

Both JSR imps return, BRAZP is taken, so TRAP executes. This causes jump to 0200, and we are starting all over again. > This is an or - loop.

Q. What is the content of R2 just after execution of the ADD instruction? Given the assumptions of the above question, will execution ever reach 0200+7+5002005

$R_2 \leftarrow R_2 + R_1$  so  $R_2 = 0201$ . The BR3 will not be taken, JSR 300 will execute and BR n3p +1 will ging over JSR 500. So PC nova has 0700 (but wouldn't anyway because jump & in to 0205+500=0705) Q. Suppose Memory[0025] = (211 20). Will the program's execution ever cause a transition to state 13? Recall the decimal=hex=binary equivalents: 10=A=1010, 11=B=1011, 12=C=1100, 13=D=1101, 14=E=1110, and 15=F=1111. The TRAP will jump to 0211, which is not local to the above code. I have no idea what is there, so can't say what will happen. But nothing in this code will cause an illegal gocode exception (opcode = 1101 = D). But, assuming 2011 is 200, Then Dood is fetched, Q. If instead Memory[0025] = 0208, will the program's execution ever cause a transition to state 13?

A jump to 208 executes a BR that is never takes because x0000 has opcode 0000 and ngp = 000. This is a NOP. Same at 0209. At 20 A is a BR PA +1 . This BRp +1 might be taken, junping x DOD at 20 B. But it might not, and an illegal opcode exception would occur. aver

Q. In all the questions above, any possibility of a transition to state 49 is ignored; that is, we assumed that interrupts would not occur. What information given above about the state of the machine guarantees that interrupts cannot occur?

The PSR. Priority = 7. No interrupt can occur because the code is executing at highest privity already.

| <b>II.</b> Suppose w 32-bit address | ASCII code            | char       |         |

|-------------------------------------|-----------------------|------------|---------|

| bit word can baddressed byt         | x30<br>x31            | '0'<br>'1' |         |

| address                             | content byte (in hex) | <br>x39    | <br>'9' |

| address  | content byte (in nex) |

|----------|-----------------------|

|          |                       |

| 12345678 | 30                    |

| 12345679 | 31                    |

| 1234567A | 32                    |

| 1234567B | 33                    |

| 1234567C | 34                    |

| 1234567D | 35                    |

| 1234567E | 36                    |

| 1234567F | 37                    |

| 12345680 | 38                    |

Because it is little-endian, if R6 = 12345678, executing these instructions,

LDR R1, R6, 0 LDR R2, R6, 1 results in, R1 = 33323130 R2 = 34333231

**Q.** Suppose we order our LC3 with the maximum amount of memory installed. What is the physical memory size in 32-bit words? In bytes?

32-bit memory addresser -> 2<sup>32</sup> locations, each referencing one Byte. => 22.230 = 4GB. 4GB(Word) => 1 GWord.

**Q.** Recall that when we send a word to the LC3's DDR (Display Data Register), only the low byte is displayed, the upper bytes are ignored. I/O is mapped to the 2^9 (512) addresses at the big-address end of memory, similarly to the original LC3 with addresses extended to 32 bits. Consider this code,

RI  $\leftarrow M[123,45678] = 33323130$   $\leftarrow x30$  gots printed  $\Rightarrow '0'$  printed = RI  $\leftarrow 1000$  digit each R3 ~ 0 AND R3, R3, 0 ;--- initialize loop counter 🛛 💦 🛩 🎖 ADD R3, R3, 8 LOOP: LD R1, R6, 0 STI R1, DDR ADD R1, R1, 1 loop: '01234567' ADD R3, R3, -1 R1 ~ 123 456 79 BRp LOOP is printed. TRAP x25 But RI always reloaded at LOOP => 01001000 ;--- Pointer to DDR DDR: .FILL xFFFFFE06 Show the display's output, assuming the output cursor was originally in the upper-left character position.

Display

8×(k(cii x30) -> 8× '0'

**Q.** What would be in R3 after execution of this program fragment?

36353433 R3 6 LDR R3, R6, 3 L shift ADD R3, R3, R3 ADD R3, R3, R3 L shift ADD R3, R3, R3 LYNFY ADD R3, R3, R3 R3 ~ 63534330 L shift

**Q.** What does the following code display?

\_ r\$ ;-- R0 <=== Mem[ R6=12345678 ] = 33323130 LDR R0, R6, 0 R4, MASK :-- R4 <=== MASK LD 0011 0011 0010 0100 010 0011 0000 R5, CNTR ;-- R5 <=== CNTR LD R4 - 0000 0000 0000 0000 0000 0000 0000 AND R1, R1, 0 :-- R1 <=== 0 LOOP: AND R3, R4, R0 ;-- is current bit 0? BRz SHIFT 🍢 mask for bit 8 if 1, add 1 to RI 0/00 1100 ADD R1, R1, 1 R1++ Ishif R1 reverses bits SHIFT: ADD R1, R1, R1 (4 A)L shift mask L shift entre ;-- if not done, do next bit & stops when R51s 1 L shifted out ADD R4, R4, R4 ADD R5, R5, R5 **BRnp LOOP** print low 8 bits of RI DONE: STI R1, DDR 🔶 ->8 shifts TRAP x25 ;-- HALT -> mask MASK: .FILL x00000 (00 ;--- Note ":" is ignored for labels. R1 gets 8 bits of RO[15:8] .FILL x01000000 CNTR: DDR: .FILL xFFFFFE06 -> prints 11'(?) but reversed -> x4A (some cha?)

**Q.** Treating VALUE as an integer variable, what is the effect of this code?

RO < 0 AND R0, R0, 0 The oldo as 2's complement, this is -5 ADD R0, R0, 1 RO ~1 ADD R0, R0, R0 LShift x0004 ADD R0, R0, R0 NOT R0, R0 FFFB LD R1, VALUE ADD R1, R1, R0 1234 ST R1, VALUE 122 F = RI VALUE -5 VALUE: .FILL x00001234 o op s, missing code! Bits of RØ are b3, b3,...b, b. Don't count? **Q.** We want to turn on the *n*-th bit L1: BRz L2 of R0, where *n* is a positive integer ADD R1, R1, R1 in R5, without changing other bits ADD R5, R5, -1  $\max_{h \in x} n = x^{3} = [8.14) + [] = 49_{10}$ of R5. What are the max and min BRnzp L1 🛃 L2: NOT R0, R0 *n* can be, and still make sense (show in decimal and hex)? NOT R1, R1 Complete the code at right. AND R0, R0, R1 Lishifts R1 to bit position R5 NOT R0, R0 Assume R1 contains 1. dops / RØ) De Morgan duel of OR Turn in bit

Voops, 2 Q. In order to get a result value of (1,) what positive value would we add to the value represented by the content of R1? Assume R1's content is a number encoded in 32-bit floating point format.

bits in R1:

Recall that the 32-bit IEEE floating-point standard has 1 sign bit, 8 exponent bits in excess-127 code, and the remaining bits as the fractional part.

$+ (+127) + 1.111 \rightarrow +2^{\circ}(1+2+4+2) = 178$ in excess 127 coche exponent = 0 heed to add 1/8 **Q.** Encode the value 1/16 in IEEE 32-bit FP format.  $- + 0.001 = + 2^{\circ}(0.001) = +2^{-3}(1.00...)$ 23 zeroes

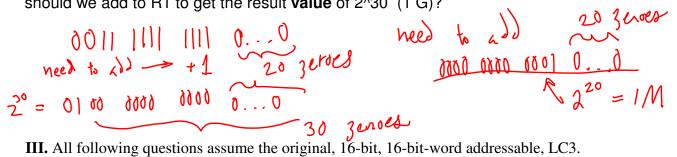

Q. The bits of R1 shown above are 3FF00000 in hex. Treated as a 2's complement number, what value should we add to R1 to get the result value of 2^30 (1 G)?

**III.** All following questions assume the original, 16-bit, 16-bit-word addressable, LC3.

**Q.** Fill in the values in the assembler's SYMBOL TABLE COUNTER 2 3000 symbol table (at right) after the first pass of assembly of this code: hot incremented VALUE STRING until 2nd line of .ORIG x3000 Counter "here " 3000 here Gode "TRAP" Symbol sets value There" 3002 there Suppose OS code at x0200 sets up the Vector Tables, sets R6=x0000,

SP point's into VT? The SP might be add ressing as I/O be add ressing as I/O durice register when an interrupt occurs. Pushing code is:

L: ADD R6, R6, -1 2 SP & FHFF, FFFE, FFFD, ... PC + PSR waites to stack, BRnzp L in Finite foop in Land .END