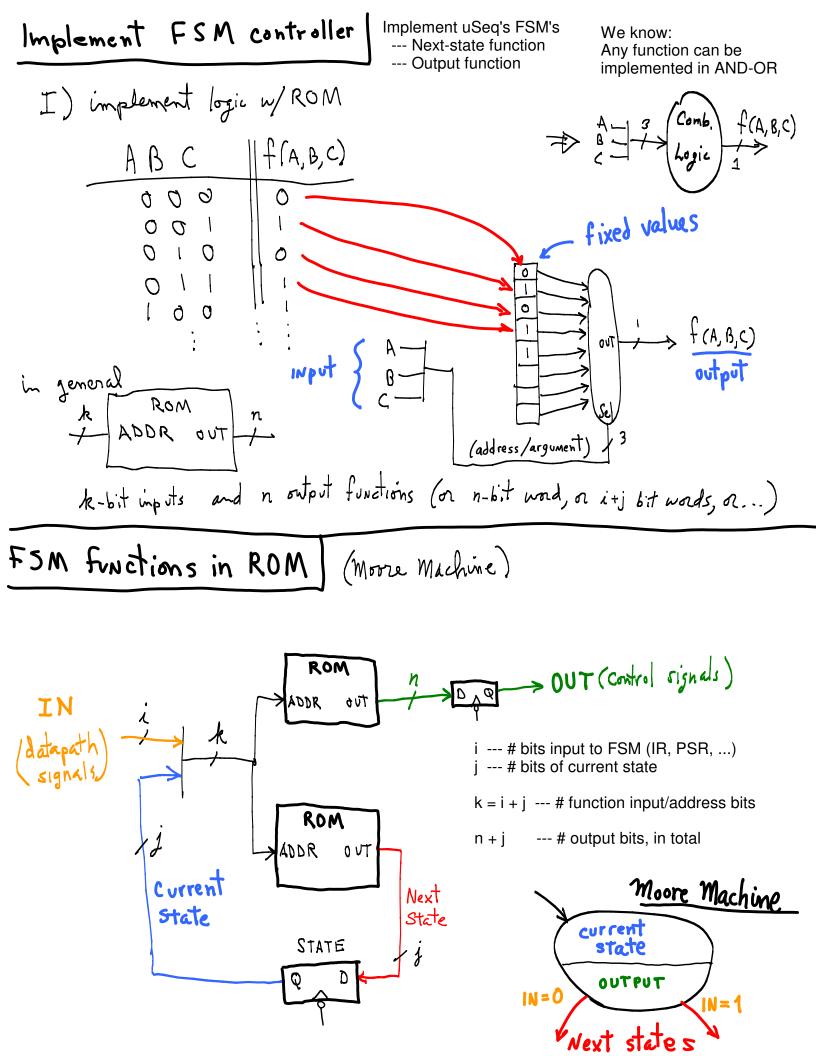

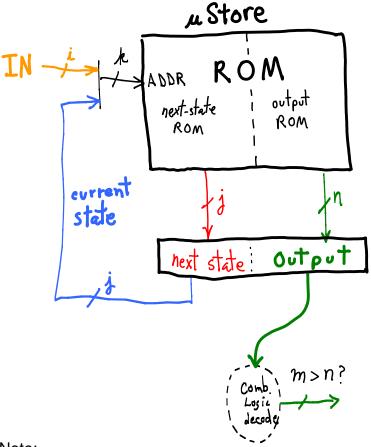

## Combine as 1 ROM

Note:

Could used control "codewords". Decode to actual control signals.

OK, if not every control bit combo is used. Saves columns of ROM.

Wasted Space?

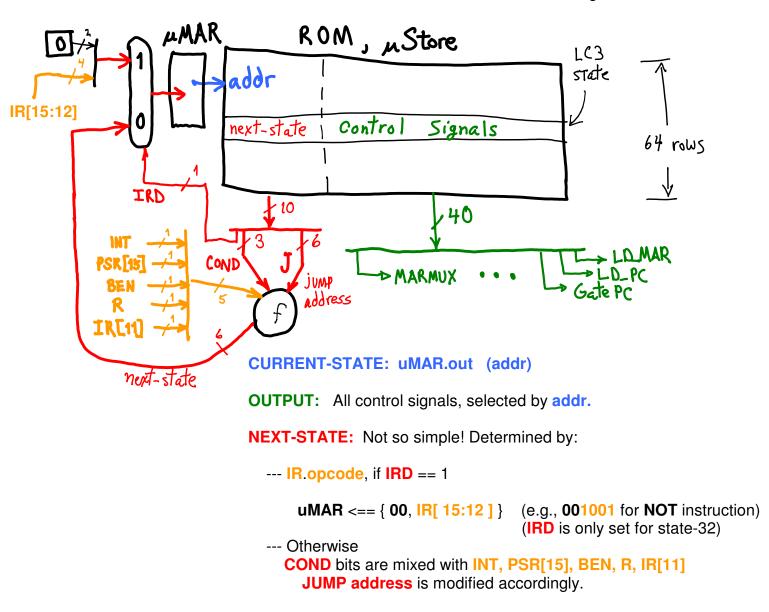

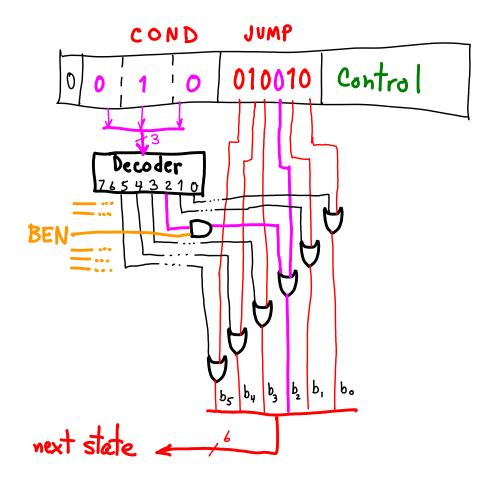

IN + current-state == (i+j)-bit address --- Many addresses ==> One LC3 state

LC3:

j = 6 (2<sup>6</sup> = 64 possible states, 59 used) i = 9 (bits input: IR, PSR, ...)

ONE LC3 state ==> (2^9 = 512) ROM rows. E.g., state-0, **BR**:

| state  | IN        | ROM address |

|--------|-----------|-------------|

| 000000 | 000000000 | x0000       |

| 000000 | 00000001  | x0001       |

| 000000 | 00000010  | x0002       |

|        |           |             |

| 000000 | 111111111 | x01FF       |

--- Uses 1-bit for next state (BEN). --- All other inputs ignored.

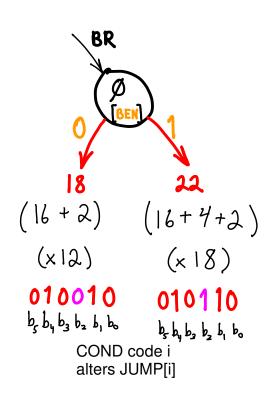

Next-state is either 18 or 22. No non-zero outputs.

--- 256 ROM rows contain 010010 0000000...000 (6+40 bits) --- 256 ROM rows contain

010100 0000000...000 (6+40 bits)

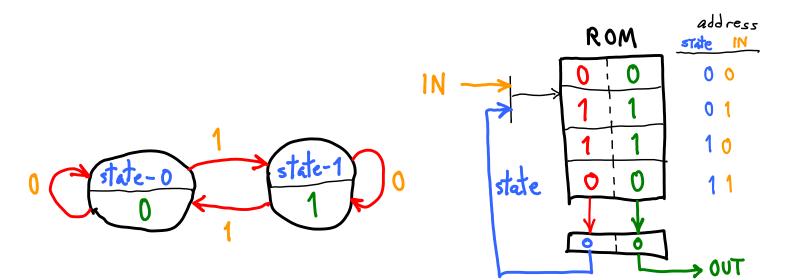

Aside: If the next state is 0, then next output is 0 (rows 00 and 11). What if that wasn't so? Would this be a Mealy Machine?

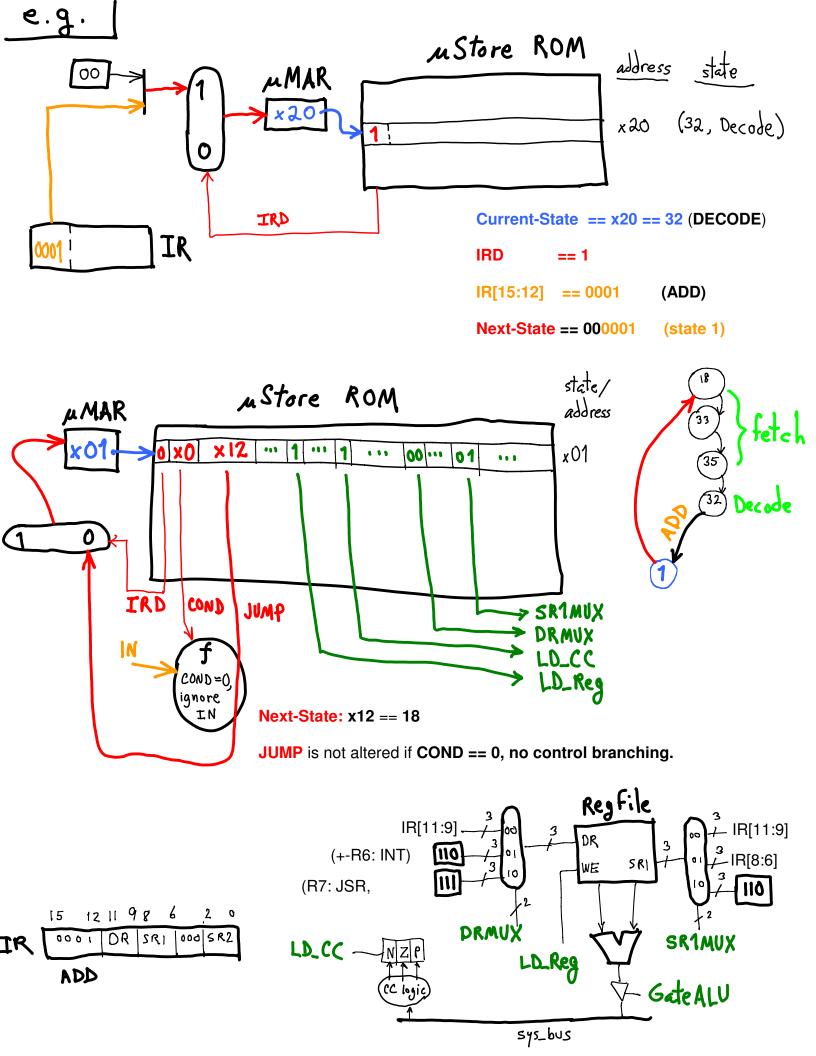

LC3 micro-Sequencer, uSeg

59 states. We need 6 bits to designate state.  $2^{6} = 64$ .

Note:

An instruction's 1st state in its execution control path is,

00xxxx,

where xxxx = IR[15:12] is its opcode.

No other states have 00 as a prefix.

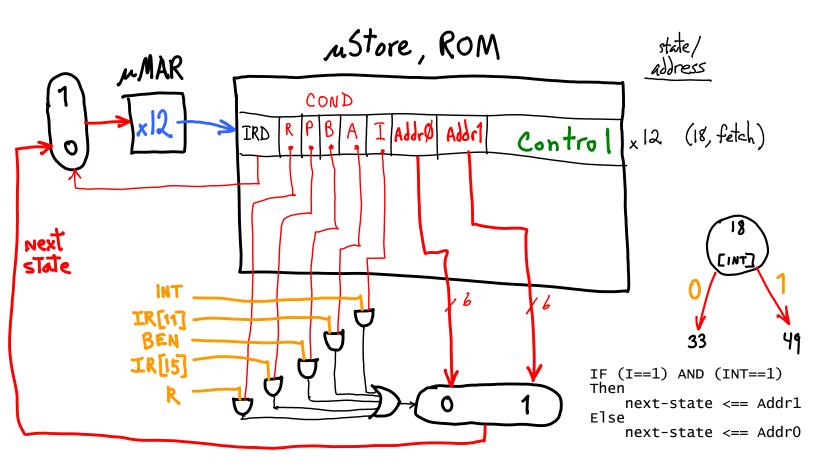

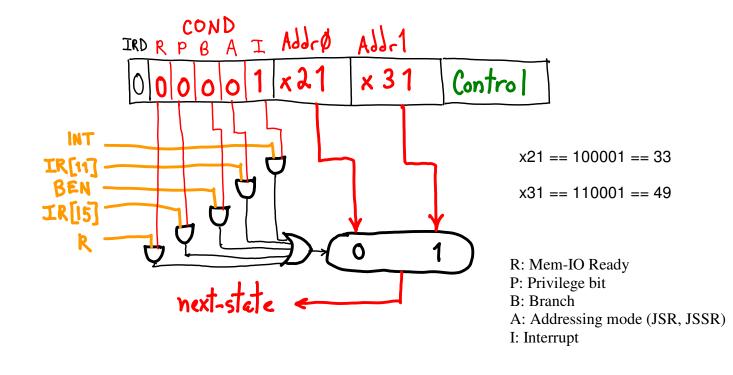

# Control Branching in LC3

But first, an easier method.

Let's have 2-way branching (except state-32).

Fields for both targets.

1-bit of input determines next state.

### Actually, in P&P

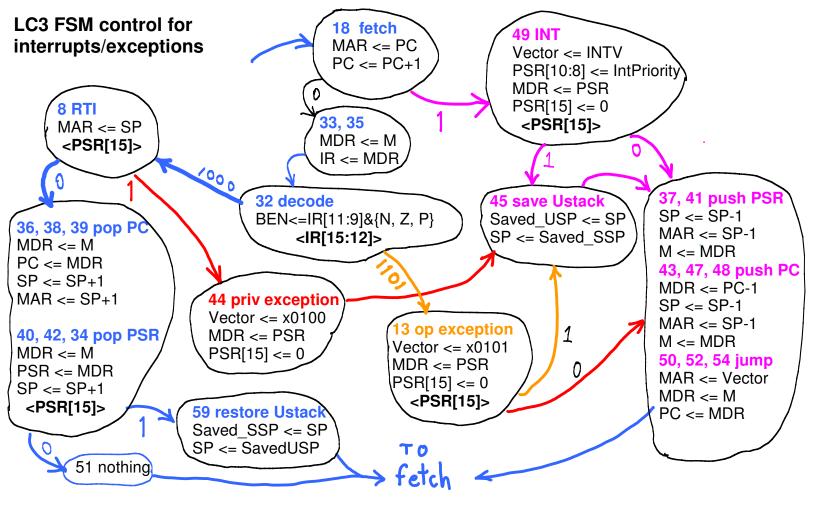

Hardware Additions (privilege + memory protection). (low-cost additions)

- **1**. TRAP switches to supervisor mode.

- 2. Return switches back to user mode.

Have TRAP act like exception? Use RTI for return?

**1.A** TRAP's state-15 acts like state-13 (opcode exception), except for jump:

Vector <== sys\_bus <== MARMUX <== ZEXT <== { x00, IR[7:0] } MDR <= PSR PSR[15] <= 0

**1.B** Branch on PSR[15]: same as state-13's: to 37 or 45 (into interrupt chain). [Unused states: 15, 28, 30.]

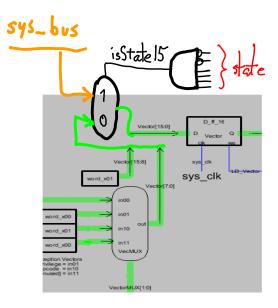

**1.C** mux Vector's input:

select = 0: the usual input

select = 1: sys\_bus

Control logic?

Don't redesign uStore to have more columns?

a. Add uSeq output "state" (controller's current state).

b. select == AND(x0F, state) [6-bit AND: select == 1 if state-15]

c. caveat: a problem for pipelining?

#### **MORE ADDITIONS** (low cost?)

#### **Disable INTERRUPTS?**

- --- A. handler needs time to set up its state before allowing a new interrupt.

- --- B. handler needs to disable multiple interrupts on same device.

#### We have:

| Interrupt:<br>Priority Comparator:                                                | PSR.Priority <== 2b'111<br>(IntPriority > PSR.Priority)                                                                                       |

|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Effect:                                                                           | All interrupts are disabled initially on interrupt.                                                                                           |

| LDI R1, KBSR<br>LD R2, BIT_14_M<br>AND R1, R1, R2<br>STI R1, KBSR<br><br>KBSR: .F | ce-status-register[14] <== 1b'0<br>IASK<br>; There is also an "OR" macro, see src/lc3pre.<br>FILL xFE00<br>FILL xBFFF ; (1011 1111 1111 1111) |

Oh, ok, we've already handled this.

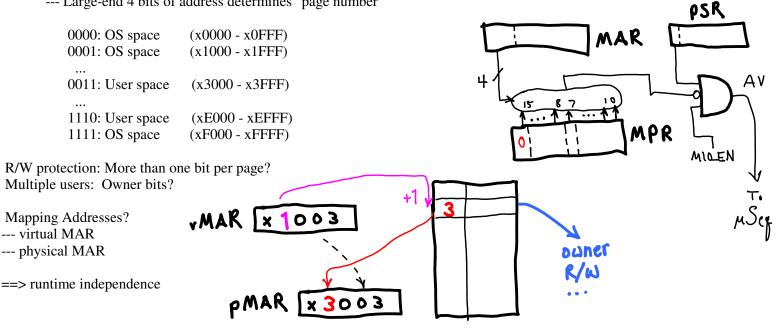

#### **Memory Protection?**

- --- Privileged status is nice.

- --- Useless unless memory is protected.

#### Need:

- --- Hardware to detect address + protection bits

- --- Exception for access violation

#### Add:

- --- MPR, Memory Protection Register?

- 16-bit addresses, 16-bits in MPR,

--- divide into 16 "pages", one bit in MPR per page:  $(2^{16})/(2^{4}) = (2^{12}) = 4k$  words per page.

- --- 0: super only, 1: user or super.

- --- Large-end 4 bits of address determines "page number"