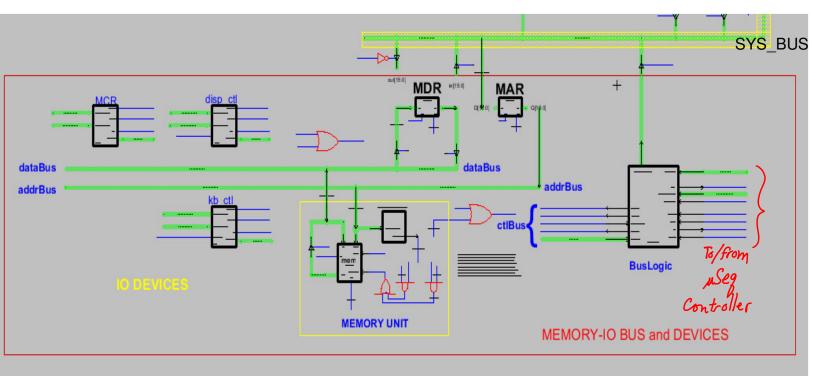

## disp\_ctl, The Display Device I/O Interface

ctl\_Bus

What is Non-Memory Mapped I/O?

--- Separate opcodes and address space (Intel x86 IA-32 and IA-64 ISAs):

in r4, x0D

--- Control-Bus signal "IO": 0, access memory; 1, access I/O device (uses same address wires)

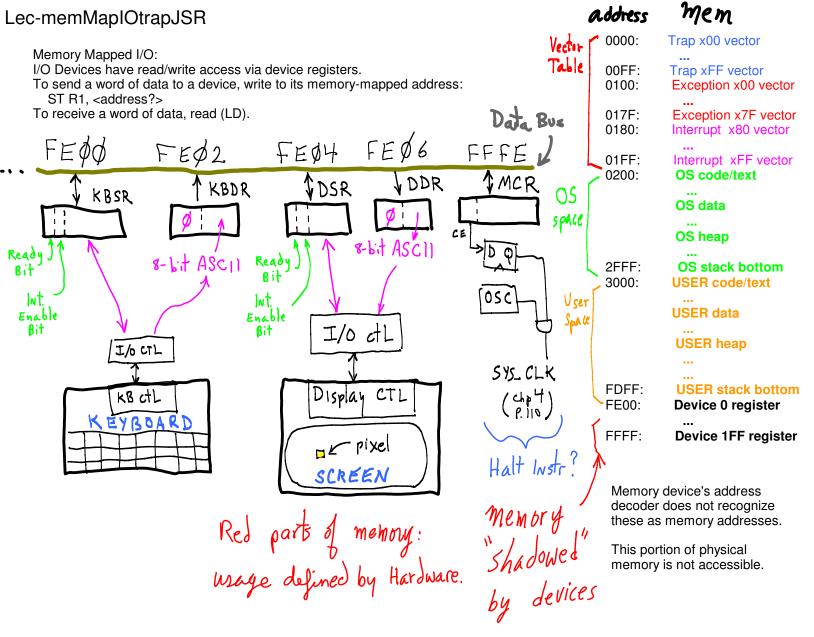

How do we know data register has valid data? Ask! Ask whom? Device's status register.

(Later: have the status register alert us instead.)

KB device controller sets Ready bit when new data is available. Clears it when KBDR is read.

POLL:

LDI R1, KBSRptr

BRn Ready BRnzp POLL

Ready:

LDI R0, KBDRptr

**BRnzp DONE**

KBSRptr: .FILL xFE00 KBDRptr: .FILL xFE02

DONE:

;--- (do other stuff)

Rdy KBSR

continue

## LC3 Operating System I/O functions Depends on OS version.

| TRAP <n></n> | Assembly-ps | bescription                                                                             |

|--------------|-------------|-----------------------------------------------------------------------------------------|

|              |             |                                                                                         |

| TRAP x25     | HALT        | jump to OS w/ message, loops in OS forever.                                             |

| TRAP x20     | GETC        | one char in, keyboard data ==> R0[7:0] (clears R0 first).                               |

| TRAP x21     | OUT         | one char out, R0[7:0] ==> display; ignores big-end byte, R0[15:8].                      |

| TRAP x22     | PUTS        | string out, $Mem[R0++] ==> display until x0000$ . Ignore big-end byte, 1 char per word. |

| TRAP x23     | IN          | displays prompt, then one char in ala GETC.                                             |

| TRAP x24     | PUTSP       | same as PUTS, but packed (2 chars per word, little-end byte then big-end byte).         |

See PP, Append. A.4, Table A.2

Who wrote this code? Which OS code is loaded into PennSim? Does Ic3as translate "HALT", "halt", ...? Who wrote Ic3as? Does every assembler for LC3 do the same thing?

Suppose:

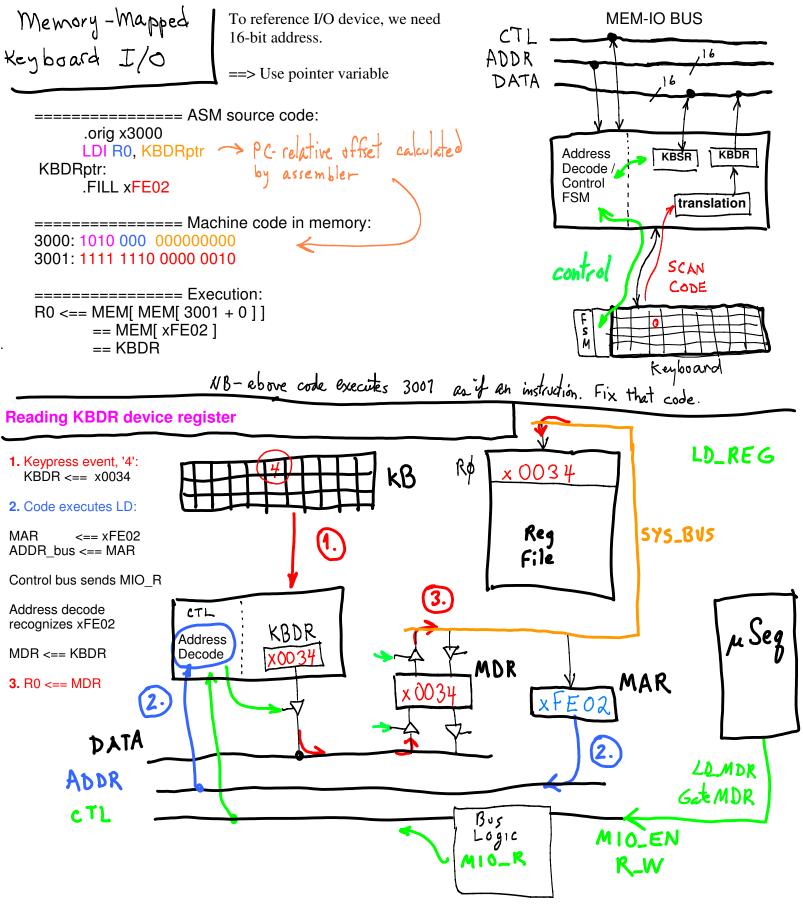

PC == 1000 Memory

...

1000: LDI R1, (+1) 1001: BRnzp (+1) 1002: FE00 instruction fetch:

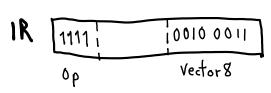

**IR** <== 1010001000000001

**PC** <== 1001

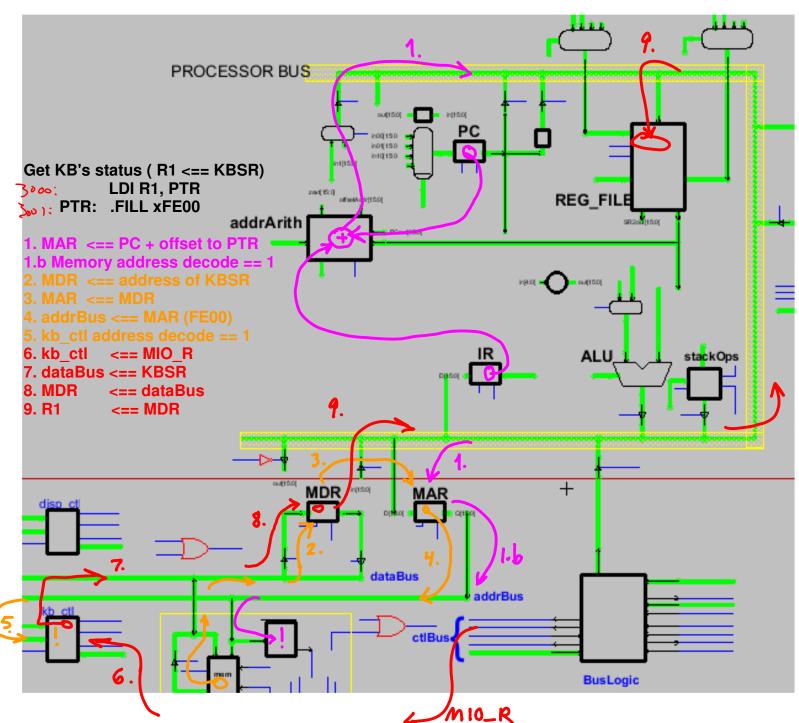

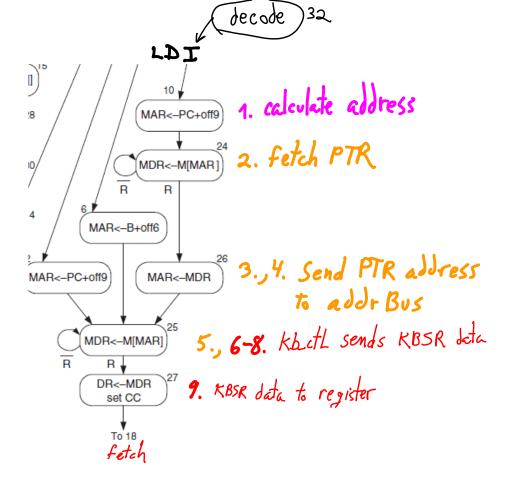

1. calculate address:

$MAR \le PC + IR[8:0] (1001 + 1)$

2. fetch PTR's data from memory: MDR <== Mem[1002] == FE00

3, 4. send address to addrBus:

MAR <== MDR (FE00) addrBus <== MAR

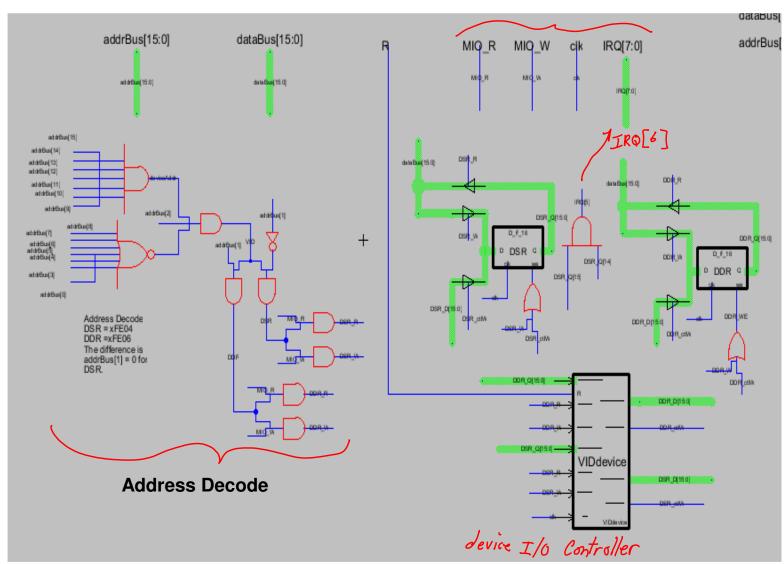

- 5. kb\_ctl recognizes address: addrBus[15:0] == 7'hFE00

- 6. uSeq Controller sends Read MIO\_R == 1

- 7. kb\_ctl sends KBSR to dataBus dataBus <== KBSR

- 8. MDR gets KBSR data: MDR <== dataBus

- 9. KBSR data to destination register:

R1 <== sys bus <== MDR

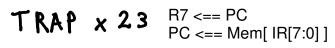

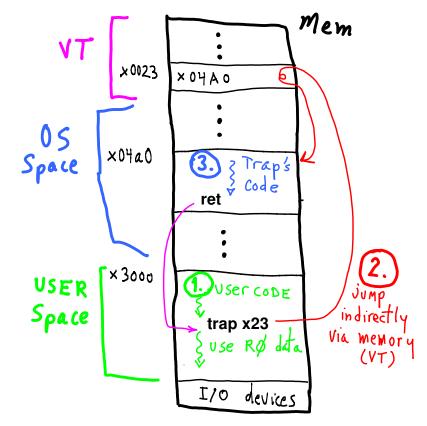

## Trap instruction execution

TRAP routines provide services.

User (and OS) code jumps to Trap's code to use service.

- 1) USER CODE

executes Trap

- 2. jump: PC loaded from VT

- 3. Trap service code executes

- 4. ret executed

"ret" = "jmp R7"

(PC

R7)

```

TRAP ROUTINE USAGE

Saving/Restoring Regs

```

.END

Whose job is it to save/restore registers and state? Depends:

-- Register? ==> caller or callee? by convention.

-- PC, CC/PSR? ==> hardware

-- stack SP? ==> hardware/OS/user code.

```

Here, convention is called saves

;= Trap x23 Routine (aka "IN")

Stated in OS's documentation

.ORIG x04a0

; == code's runtime location.

Display prompt

;== save user's registers.

st r1, saved_r1

<== char

st r2, saved r2

DSDR <== r1

;== get input

Read 1 char from kb

r2 <== KBSR

ld r1, saved_r1 ;== restore user's registers.

poll

ld r2, saved r2

r0 <== KBDR

ret

;== return to user's code

saved_r1:

.FILL x0000

;== reg value storage

saved r2:

.FILL x0000

;== reg value storage

```

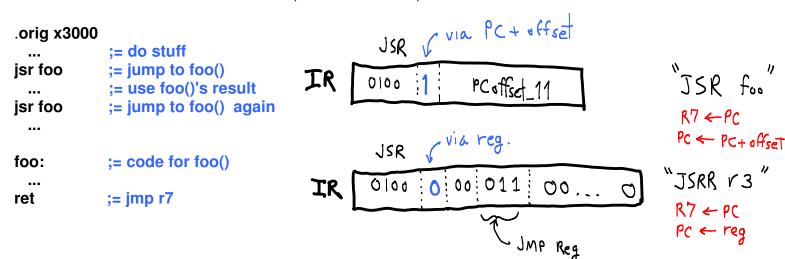

USER-LEVEL "TRAPS" i.e., Sub-routines

Reuse code.

Who (caller/callee) is responsible for saving/restoring registers?

If code is generated by compiler? ==> by compiler convention.

(What about CC?)

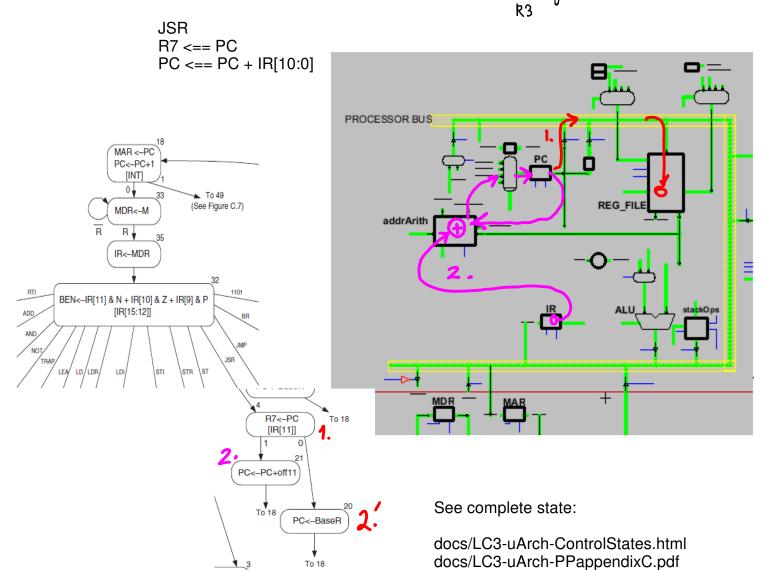

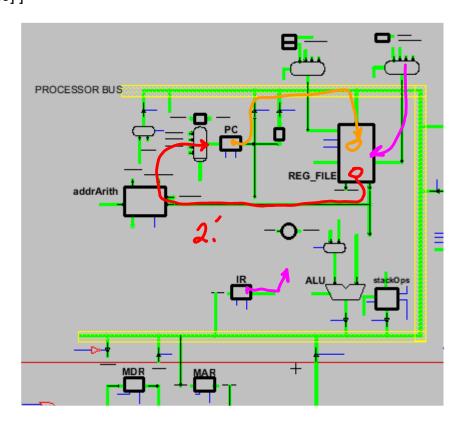

JSSR R7 <== PC PC <== RegFile[ IR[8:6] ]

OK, So far, so good, BUT

What about passing arguments and return values?

What about nested calls, recursion?

Generally, saving state involves more than RegFile:

PSR[15] = Privilege level (1=user, 0=super) PSR[10:8] = Interrupt Priority level (0=low, 7=high)

PSR[2:0] = CC(N, Z, P flags)

Also, there are usually other important bits in PSR (but not for LC3). Also, there are other status and control registers (but not for LC3).

## Puzzlen, PP Fig. 9.8 (see Fig.s C. 2+C.7, FSM states for Trap)

;========= ;= Trap x23 (aka "IN") :==========

.orig x04a0

st r7, saved\_r7 jsr save\_regs

save\_regs: st r1, saved\_r1 st r2, saved\_r2

st r6, saved\_r6 ret

saved\_r1: .FILL x0000 saved\_r2: .FILL x0000

---

saved\_r6: .FILL x0000 saved\_r7: .FILL x0000

In PP's Fig. 9.8,

Why isn't "st r7, saved\_r7" inside the routine "save\_regs"?

Does this mechanism work for nested calls?

Could we use the stack instead?

Why not "jsr save\_regs" before "st r7, saved\_r7"?

where did this Trap x 23 "IN" code come from?

If its' in OUR LC3 memory,

how did it get there?

Where can I find the source code for the trap x23 routine?

- (1) run PennSim.jar or lc3sim or Simulate.exe,

- ---- look at VT, at address x0023

- ---- see what address is stored there

- ---- look at code at that address

- (2) see OS source code in src/lc3os.asm