See P&P Appendices A and C: LC-3 ISA, TRAPS, Devices, Interrupts, Exceptions.

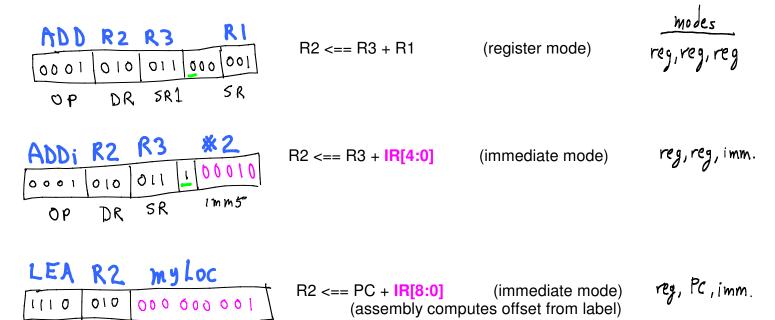

1. DATA IS IN REGISTERS (RegFile[ i ] , IR , PC)

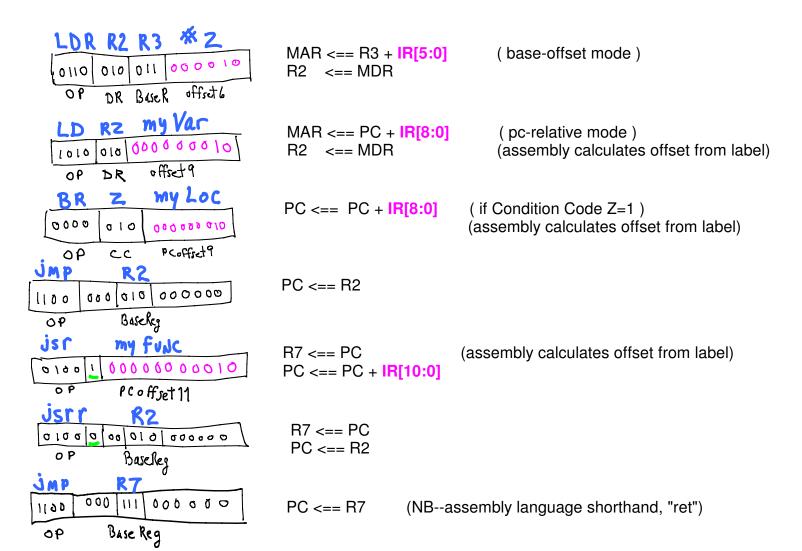

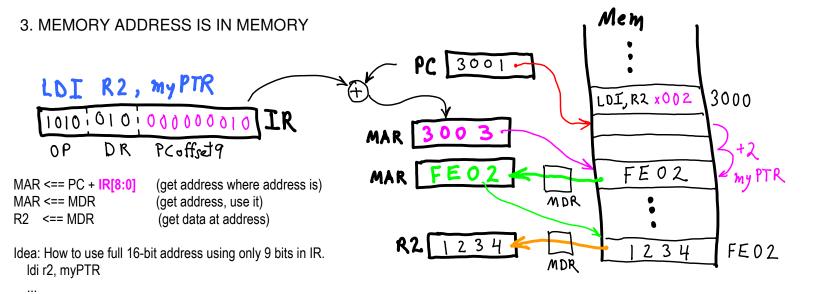

2. MEMORY ADDRESS IS IN REGISTERS (Regfile[ i ] , PC , IR)

PC offret 9

DR

OP

Alternative: Move myPTR into a register, use base-offset mode: Id r1, myPTR

ldr r2, r1, 0

myPTR: .FILL xFE02

myPTR: .FILL xFE02

Alternative: Move VT entry into a register, use jssr: Idi r1, VT2 jssr r1

VT2: .FILL x0002

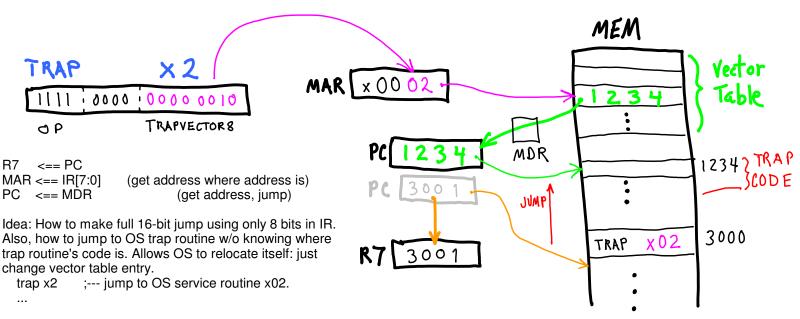

Note: Using what we had above to eliminate ldi, we could eliminate both LDI and TRAP instructions from the LC3's ISA: we would have two unused opcodes to play with.

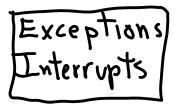

Yet another address-in-memory mechanism. Just like TRAP, but not an instruction.

Something goes wrong: jump to OS routine (exception) I/O device sends a signal: jump to OS routine (interrupt)

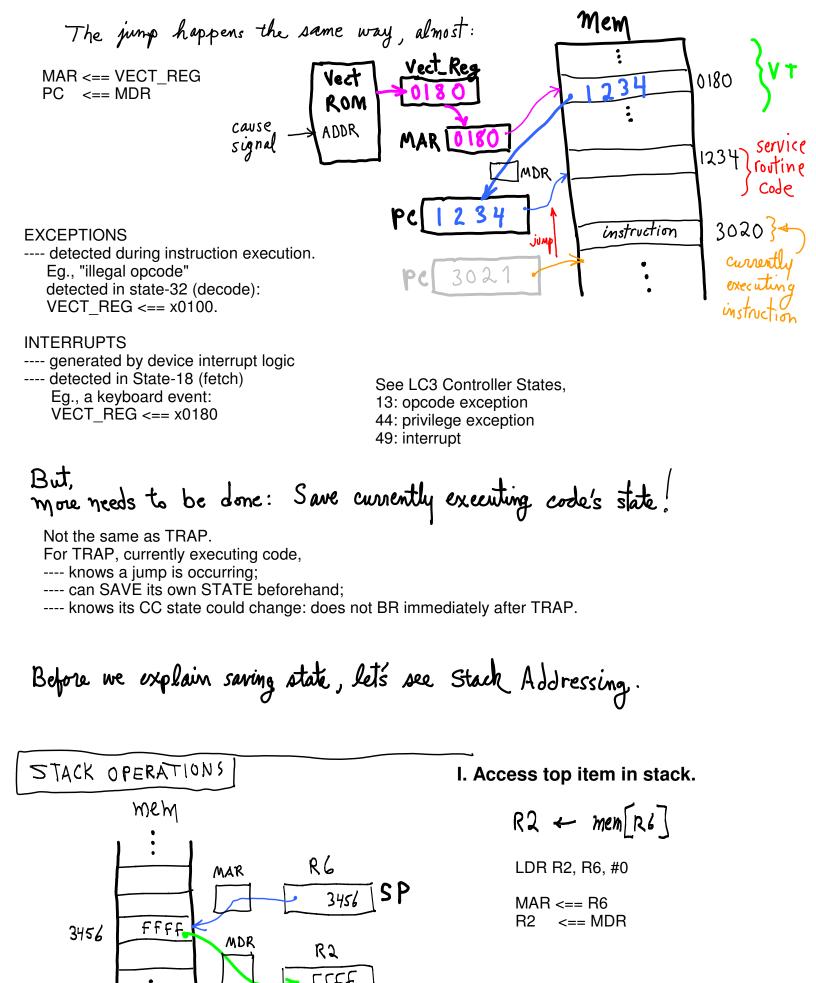

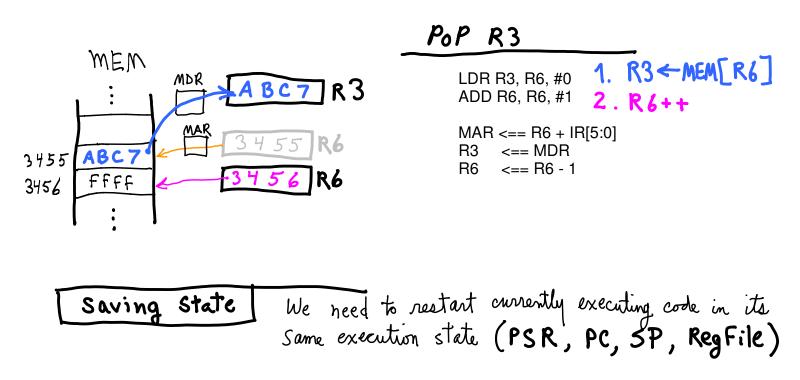

Stack Pointer (SP) is R6

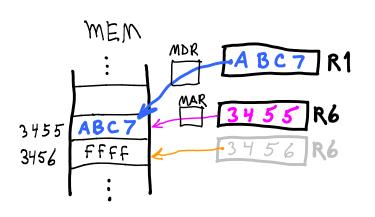

## II. Put new item on top of stack: PUSH

## PUSH R1

ADD R6, R6, #-1 **1. R6**--STR R1, R6, #0 **2.** MEM [R6] ← **R1**

R6 <== R6 - 1 MAR <== R6 + IR[5:0] MDR <== R1

III. Remove item from top of stack: POP

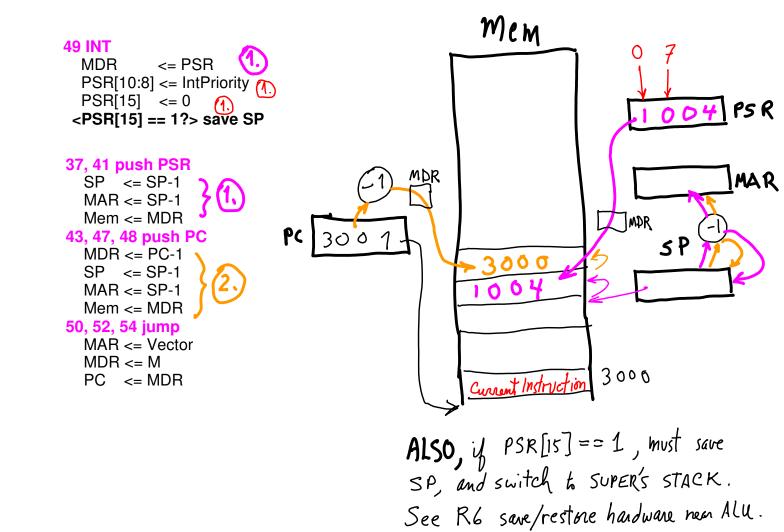

When an exception/interrupt occurs

- ---- The PSR gets altered immediately, before the next instruction is fetched.

- ---- The PC gets altered, i.e., a jump.

- ---- PC could go to R7, but what about nested execeptions/interrupts?

- ---- The SP (R6) is used to save state, it needs to be saved.

- ---- Regs can be saved by service routine code.

- ===> Hardware, not instruction execution, must save state!

When exception/interrupt routine COMPLETES

--- RESTORE Regs, done in software

--- RESTORE PC, PSR: the RTI instruction:

PC <== POP PSR <== POP

---- RESTORE SP, see R6 save/restor hardware

8 RTI MAR <= SP

## 36, 38, 39 pop PC

MDR <= Mem PC <= MDR SP <= SP+1 MAR <= SP+1

## 40, 42, 34 pop PSR

MDR <= Mem PSR <= MDR SP <= SP+1 <**PSR[15] == 1?> (restore SP)**

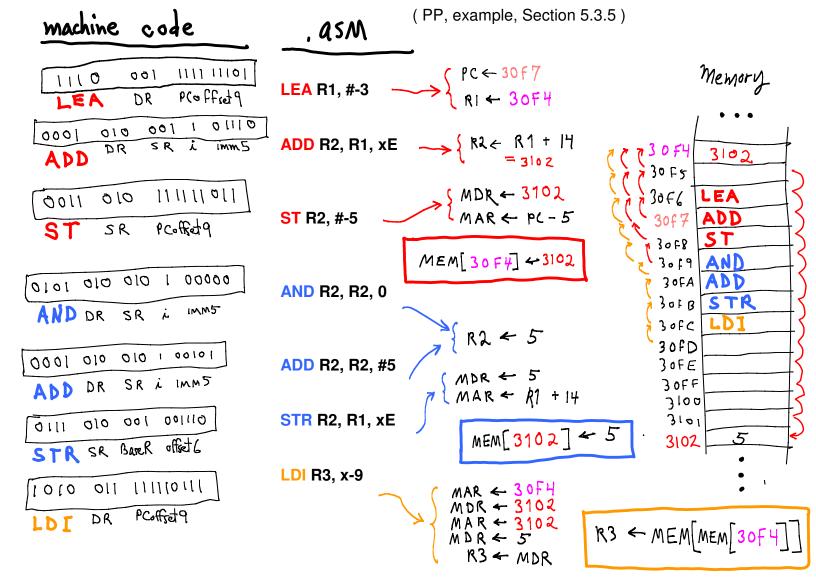

| ; R1      | <== &pointer | R1 gets (address of pointer variable)                                       |

|-----------|--------------|-----------------------------------------------------------------------------|

| ; R2      | <== &data    | R2 gets (address of pointer variable $+ 14$ ) == (address of data variable) |

| ; pointer | <== &data    | pointer variable gets (R2, address of data variable)                        |

| ; R2      | <== 0        | data calculation into R2                                                    |

| ; R2      | <== 5        | data calculation into R2                                                    |

| ; data    | <== 5        | MEM[(R1, address of pointer variable) + 14] gets data, R2                   |

| ; R3      | <== data     | R3 gets data from MEM via de-referencing pointer variable.                  |