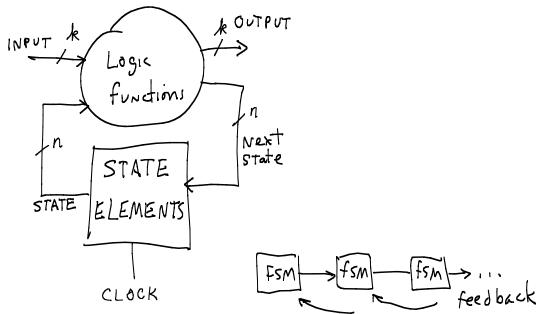

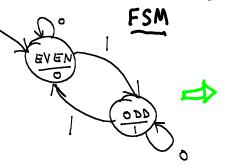

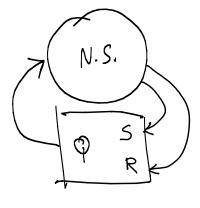

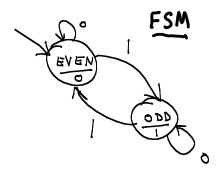

FSM has input/output, but from/to where?

- (1) Other FSMs in same machine

- (2) Feedback loops

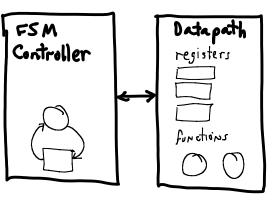

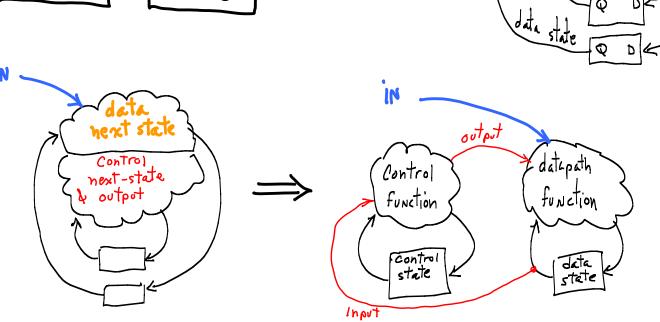

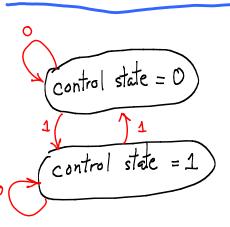

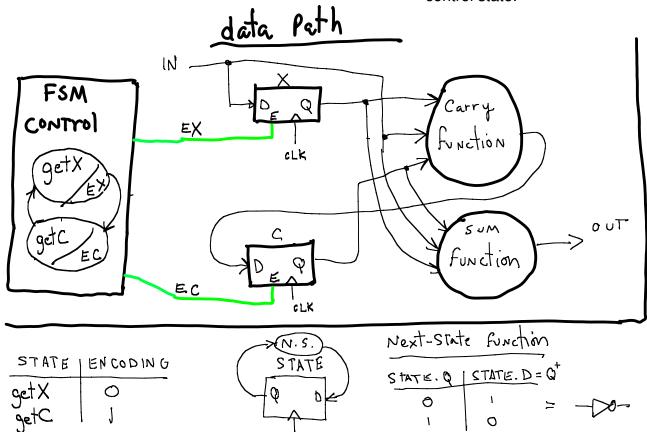

We like to separate state into two "types", control and data state. Eg., some state elements are for "control" state, and some are for "data" state.

control state/

D

#### Total machine state

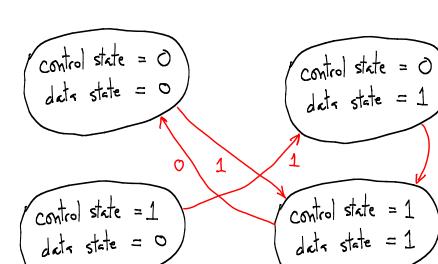

Suppose a FSM with 1-bit controlstate element and 1-bit data-state element. Total is 2-bits of state; 4state machine. State diagram quickly becomes a mess. What if 2-bit data-state? 8-state total FSM, but only 2 control states.

Splitting state:

"datapath state"

In any control state, data state can be in either of two states: 0 or 1. Data states could be much larger: using just one 32-bit data register gives us 4 G data states. With this 2-state control, total machine state would be 8 G states.

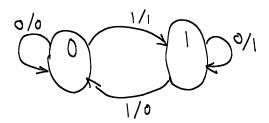

Serial parity but machine

| STATE | EN CO D | n N G |

|-------|---------|-------|

| EVEN  | Q =     | D     |

| 000   | Q =     | 1     |

|       | •       |       |

| O DI | or<br> | =     | \   |

|------|--------|-------|-----|

| '    | OR     |       | 1   |

| EVEN | Q.=1   | 6'= a |     |

| 000  | @,=0   | Q.= ( | - 1 |

|      | , , ,  | • • • |     |

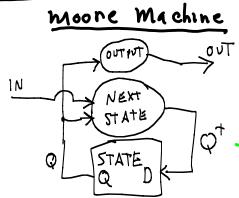

#### Next-State function

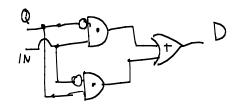

#### Next-state circuit

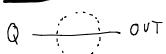

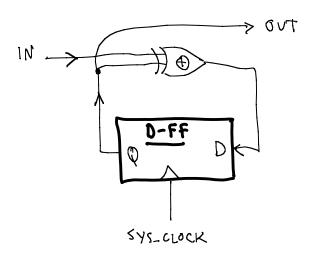

# $\frac{Q \mid 0 \lor T}{Q \mid Q} \quad 0 \lor T = Q$

**Function**

$$D = \overline{Q} \cdot IN + Q \cdot \overline{IN}$$

#### OUTPUT CITCUIT

That was easy, but hey! No imputs! co

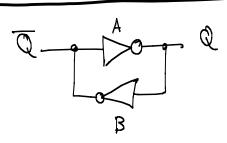

Supposa A.out = 0 B. out A. out = 0Stable!

A.out = 1 → B. out = 0 → A. out =1 STable

Q = 1 Q = 0 states! hooray!

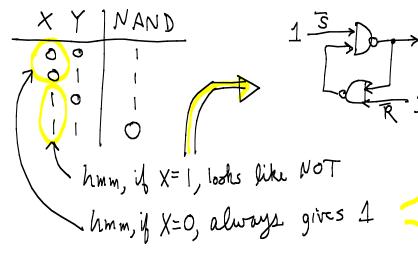

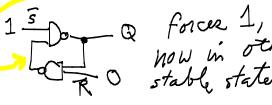

The state is latched (captured) when -S = -R = 1. NAND-NAND latch

we use inputs? this is still a NOT

| SR  | STATE                                                                            |

|-----|----------------------------------------------------------------------------------|

| 1 1 | 1NV-INV LOOP, 2 possible states: Q=0 or Q=1<br>1-INV Loop, 1 possible state: Q=1 |

| 0 1 | 1-INV Loop, 1 possible state: 0=1                                                |

| 1 1 | INV-INV Loop, latched state Q=1                                                  |

| 10  | INV-1 Loop, one possible state: Q=0                                              |

| 1 1 | INV-INV Loop, Latched state Q=0                                                  |

Yay! State element w/ input!

Can we use this for a FSM state element?

Oh No!

-> to output -> state change! any input change -

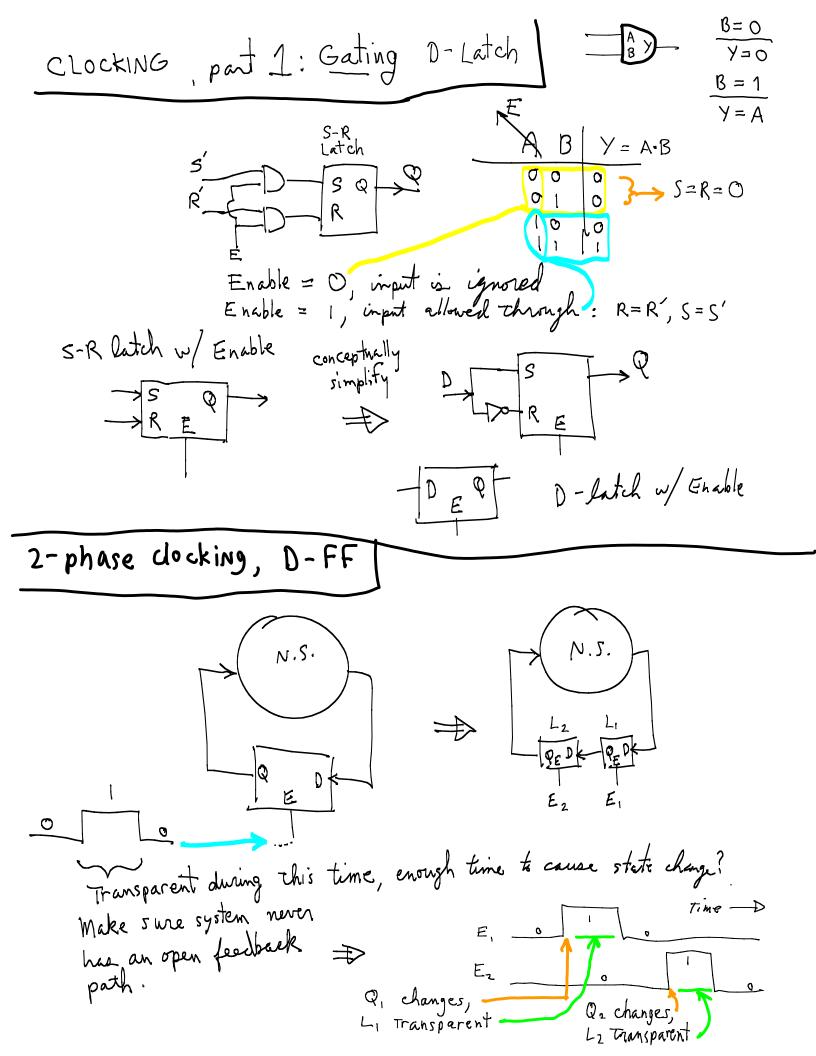

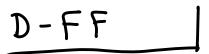

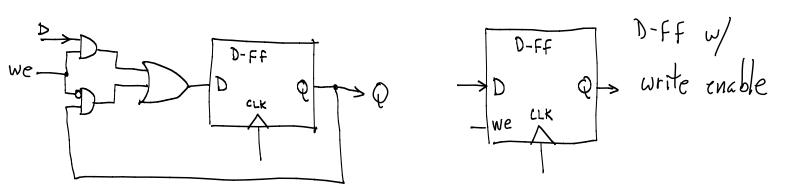

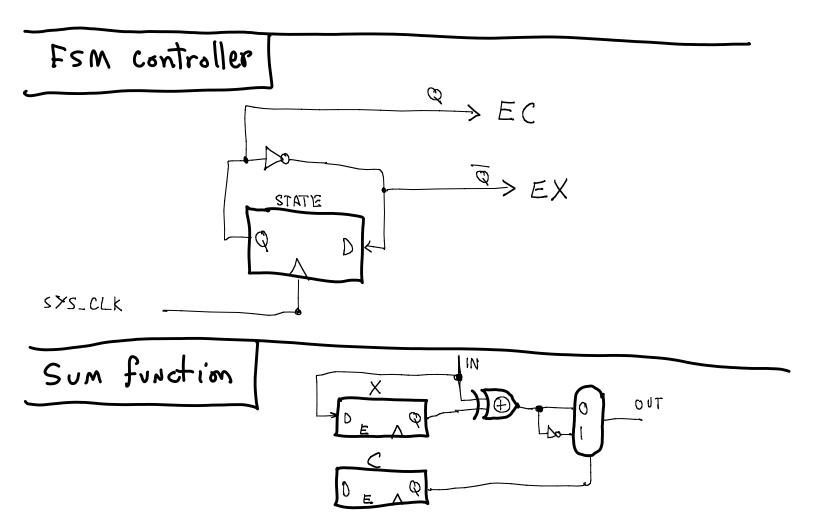

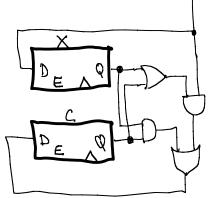

We often want to control whether or not the FF will be written into when the clock pulse arrives: add an "enable" input. When enable is 0, the current state is written back into the FF. Otherwise, D is written.

If there is no feedback path from Q to D, we do not need a flip-flop, we can use a write-enable latch instead. Datapaths sometimes can use latches.

# Serial Parity, final implementation

This is a FSM with non-trivial control state and next-state function, but a trivial datapath.

Flipflop can be 2-phase clocked, in which case the "sys\_clock" signal consists of two wires.

| STATE ENCODING |       |  |  |

|----------------|-------|--|--|

| EVEN           | 6 = 0 |  |  |

| 000            | Q = 1 |  |  |

$$\frac{\text{Mext-state}}{D = IN \oplus Q} = \frac{\text{Output}}{\text{Out} = Q}$$

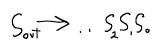

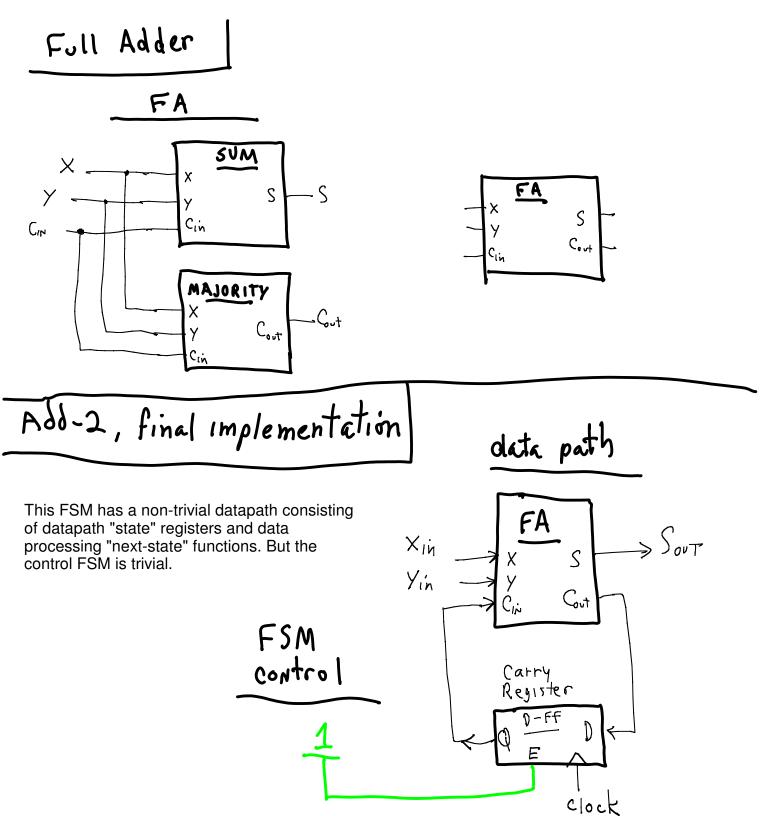

# FSM implementation, example | ADD-2, 2 serial imputs \reg.

state encoding: S0 = 1

next-state function: Q+=Q

output function: out = Q

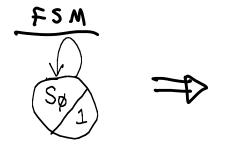

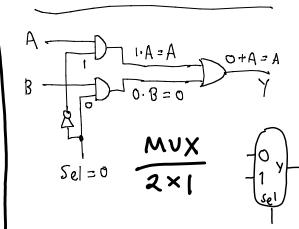

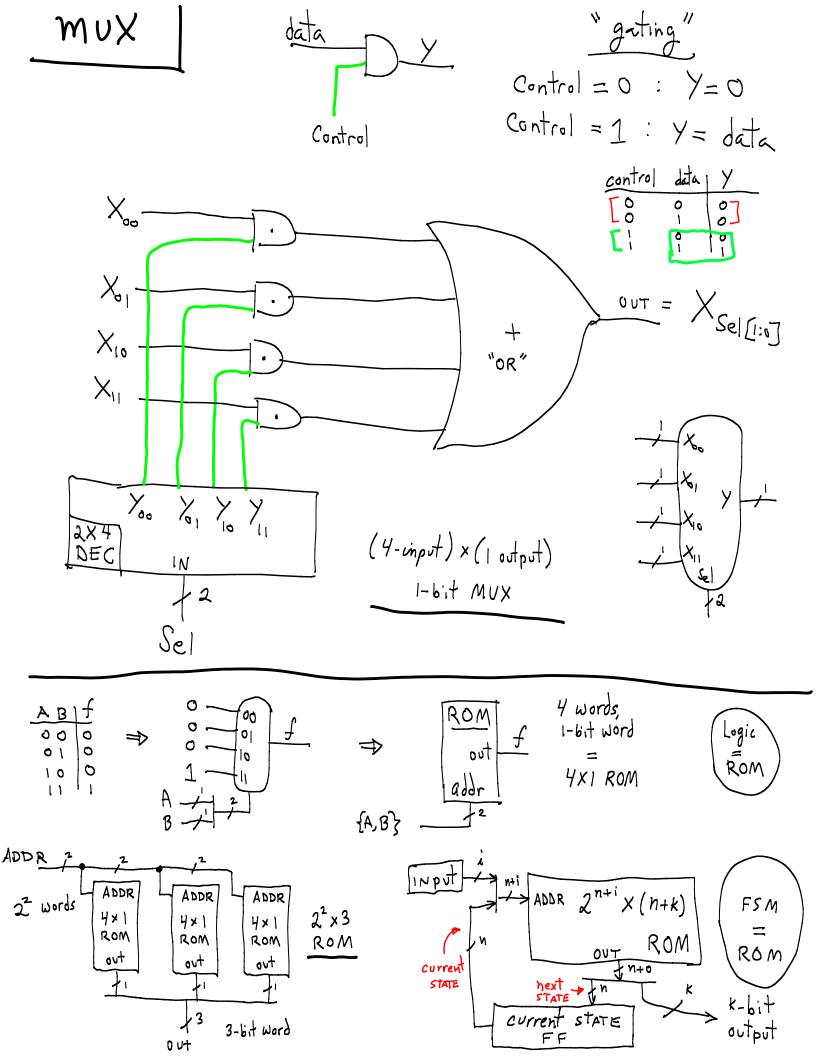

# Datapath functions, MUX

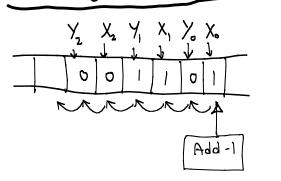

### FSM, Add-1 implementation

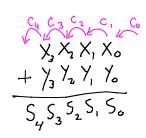

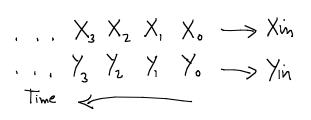

$$X = X_2 X_1 X_0$$

$$+ Y = Y_2 Y_1 Y_0$$

$$S = S_2 S_1 S_0$$

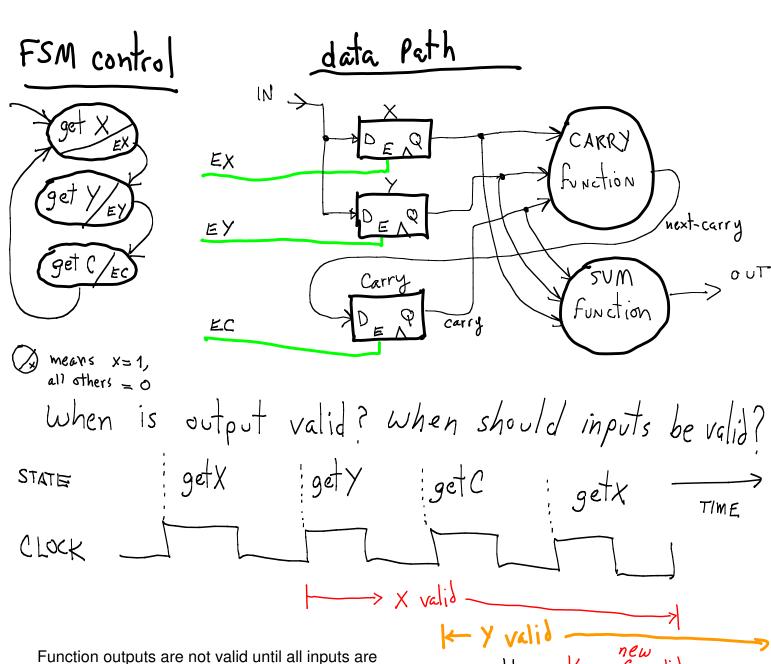

And Now, a FSM with a non-trivial controller and non-trivial datapath.

Output is only valid every 3rd clock period.

X does not become valid until clock tick that ends

available (valid).

state getX.

#### Simplified FSM and datapath

If we can depend on the input to be stable, we can eliminate the Y data register: just use the data input when it is valid for Y. Eliminates one control state.

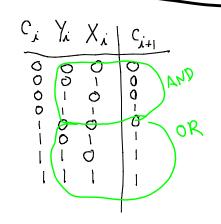

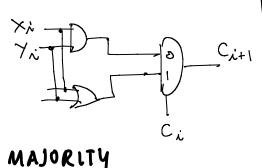

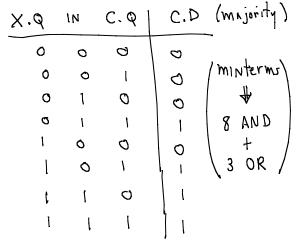

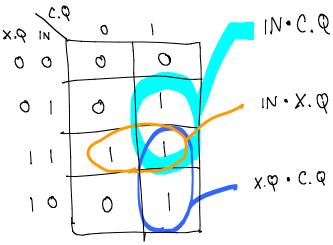

# Carry Function, w/ Karnaugh map + algebra

1 N

$$C.D = IN \cdot C.Q + IN \cdot X.Q + X.Q \cdot C.Q$$

$$= IN \cdot (C.Q + X.Q) + X.Q \cdot C.Q$$

[eliminater 3-input or]

Convert to NAND/NOR)

Q is evailable.

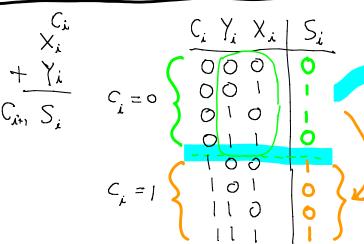

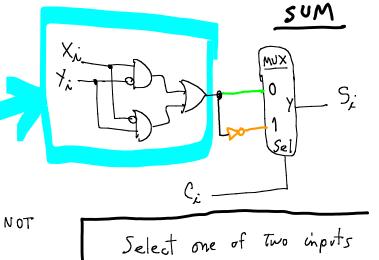

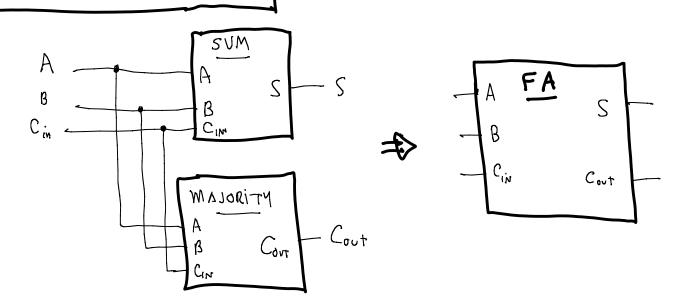

## Full Adder (FA)

# SMALLER FA circuit?

Can you find terms shared between MASORITY and SUM?

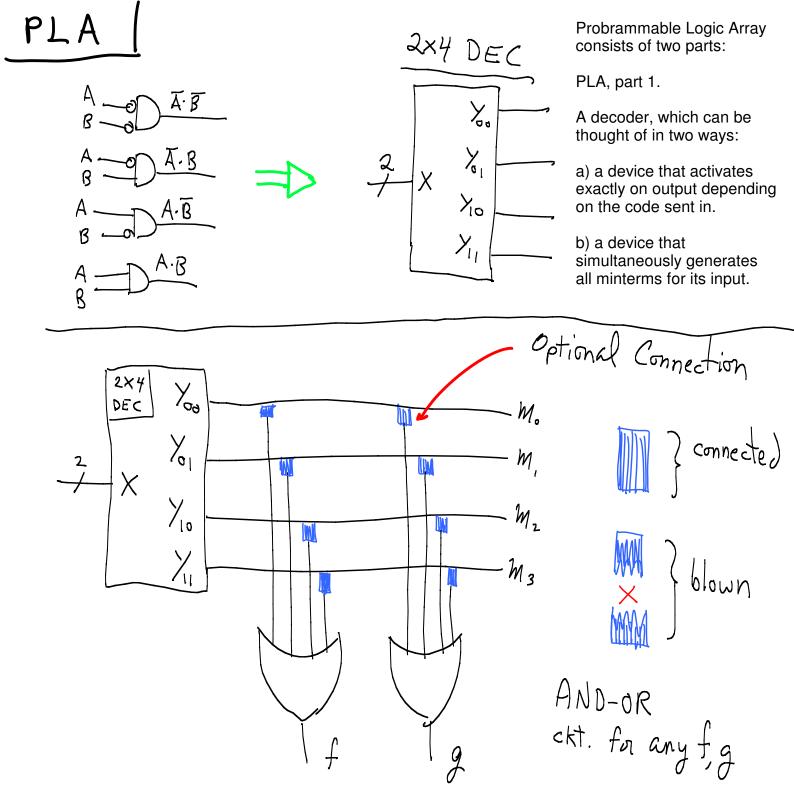

PLA, Part 2. A means of OR'ing minterms to produce function outputs.

Several ORs can share the same minterms: we can economically produce multiple functions at once.

The connections to minterm lines can be "blown" to disconnect them: this selects which minterms are included in the function.

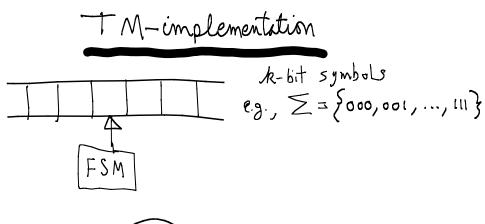

FSM in ROM ( n-bit state, i-bit input, k-bit FSM output )

(STATE, INPUT) is ROM address n bits + i bits ===> 2^(n+i) ROM locations

(NEXT-STATE, FSM-OUTPUT) is ROM output n bits + k bits ====> (n+k) bits per location

$===> 2^{(n+i)}$  location by (n+k)-bit word ROM

ANY FSM (Mealy or Moore) can be built as a ROM

NOTE: A Moore machine's output depends only on state ===> use n-bit addresses, one ROM location per state.

BUT, next-state depends on current-state+input. Encode part of next-state function in ROM word as NS-CODE, and use external logic to calculate next-state function: next-state = f( INPUT, NS-CODE ). This is what is done in the LC3's micro-coded controller.

Every possible FSM can be built as a ROM.

ROM is very large since there is a word for every possible {state, input} combination.

| Encode<br>DDE,   | addre | 55      |              | data Word | (ROW)  |

|------------------|-------|---------|--------------|-----------|--------|

| ction:<br>s done | STATE | INP JT  | next-sta     | te ou     | Tput   |

|                  | Ó     | $\circ$ | 0            |           | 0      |

|                  | Ö     | 1       | 1            |           |        |

|                  |       | Ö       |              |           | 1      |

|                  | 1     | 1       | 0            |           | 0      |

|                  |       |         | ROM          |           |        |

| INPUT            |       | 7       | State output | address   |        |

|                  | ,     | V,      | 0 0          | 5 00      | TATE 0 |

| AM               | ir lo | 0       | 1            | 10 5      | 4      |

|                  |       | next    | 0 0          | j 17 }s   | tate 1 |

|                  |       | STATE   | <b>→</b> , , | Cotate in | iput   |

|                  |       |         | output       | 21001     | •      |

We can enumerate all ROMs (and consequently all TMs/digital-computers):

Concatenate ROM content from all words:

| address | content |

|---------|---------|

| 00      | 00      |

| 01      | 11      |

| 10      | 11      |

| 11      | 00      |

|         |         |

==> 01111000

List all n = i = k = 1 machines: FSM-0, FSM-1, ..., FSM-256

List all n = i = k = 2 machines: FSM-257, FSM-258, ...

and so on.

at clock tick:

- -- { current state, current input } captured

- -- output changes to match captured state/input

- -- Every state row has same output ===> Moore Machine

- -- Rows for state S have differing outputs ===> Mealy Machine.