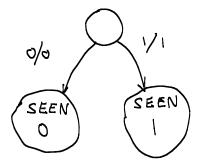

"SEEN 0" registers that we've seen a 0,

"SEEN 1" registers that we've seen a 1.

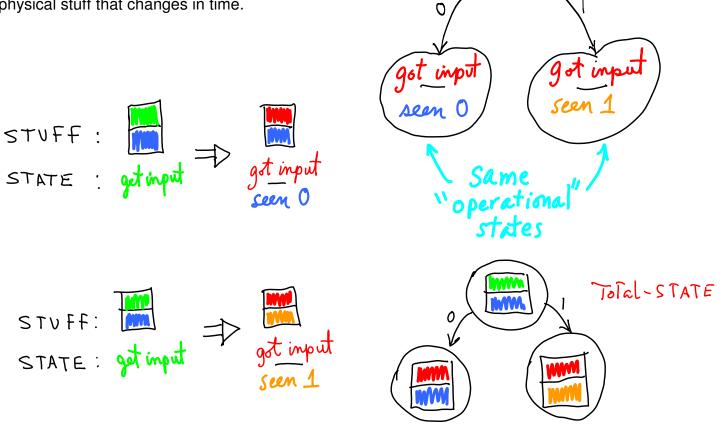

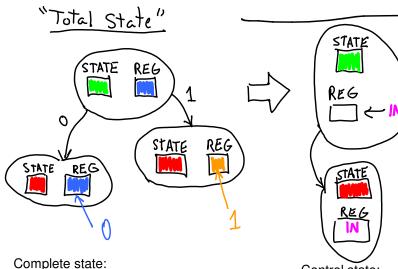

STATE has two parts:

- -- step of operation

- -- symbol seen

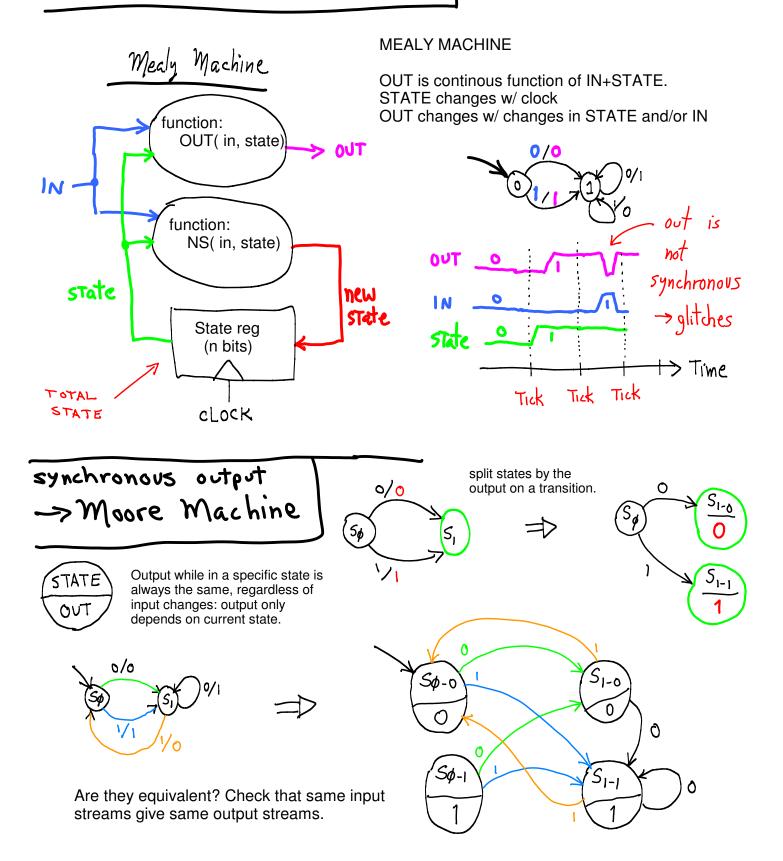

A real machine has a PHYSICAL state, physical stuff that changes in time.

TM's FSM (the CONTROL part of a TM)

No tape, one input, two outputs: -- IN-SYMBOL, OUT-SYMBOL, MOVE

For FSM, inputs/outputs are time series: 3 time: 0 1 2 4 5 6 ... input : 0 0 0 0 ... 1 1 output: 0 1 1 0 1 0 1 ... 0 move : 0 1 1 1 0 1 ...

For a physical state machine, we must talk about time explicitly, physical state changes in time.

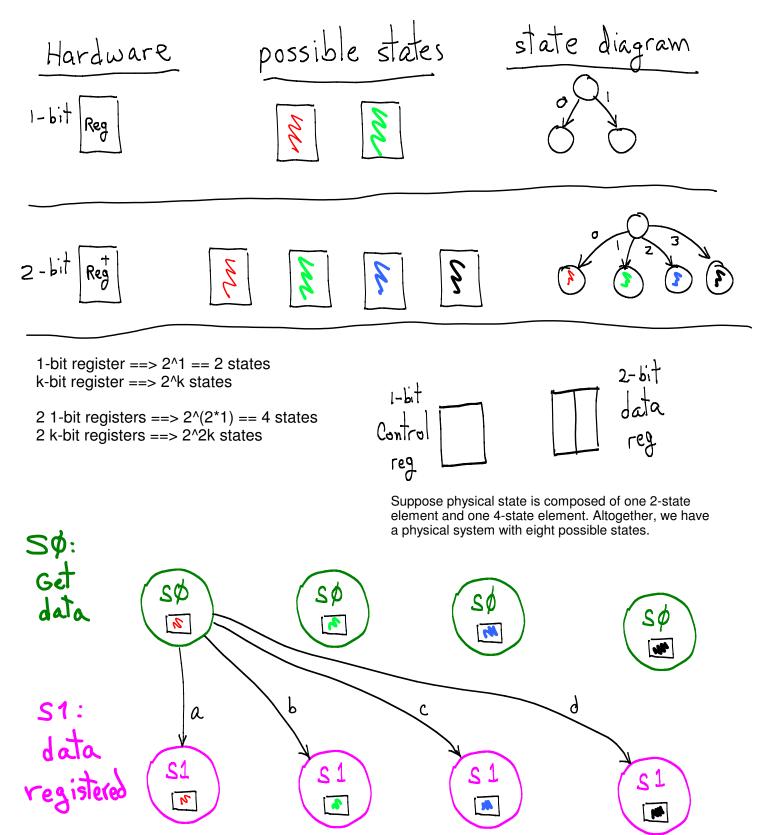

get inpJ

(2-state control) X (4-state data reg) == 8 complete states possible. Before reading input, we don't care which of top 4 states we start in, we know we have not yet registered some data: we are in the "get-data" control state. We are in the "data-registered" control state after. (What if 32-bit symbols ==> 4G branches; something we'd like to hide.)

- (1) ready-for-data-and-reg-is-zero,

- (2) got-data-and-reg-is-zero

- (3) got-data-and-reg-is-one

Control state: (1) get-data (2) got-data

next state

BIG IDEA:

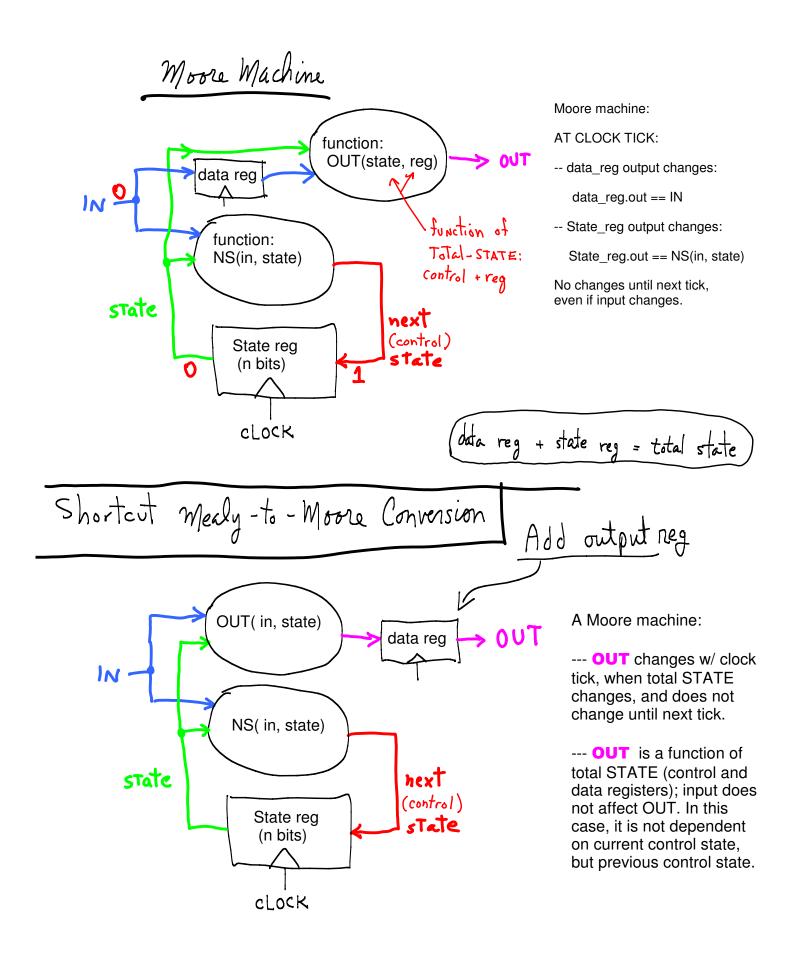

SPLIT TOTAL STATE into two parts:

--- 1. OPERATIONAL STATE Where we are in doing things

--- 2. DATA REGISTER STATE What we know at this point

registering a 32-bit input symbol :

-- TOTAL STATE: (2 Operational states) X (4G data states)

versus

-- 2 Operational states + content of reg.

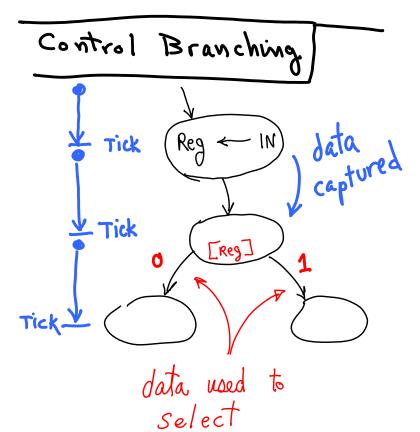

Change "operational state" depending register content.

-- States associated with Register Transfer operations (described using RTL).

-- Branches labeled w/ register content (or partial content).

CLOCK causes:

---- register data transfers ---- control state changes

USE REGISTERS for BOTH ---- "STATE" registers ---- "DATA" registers

---- BOTH types change w/ CLOCK

## Implementation of FSM

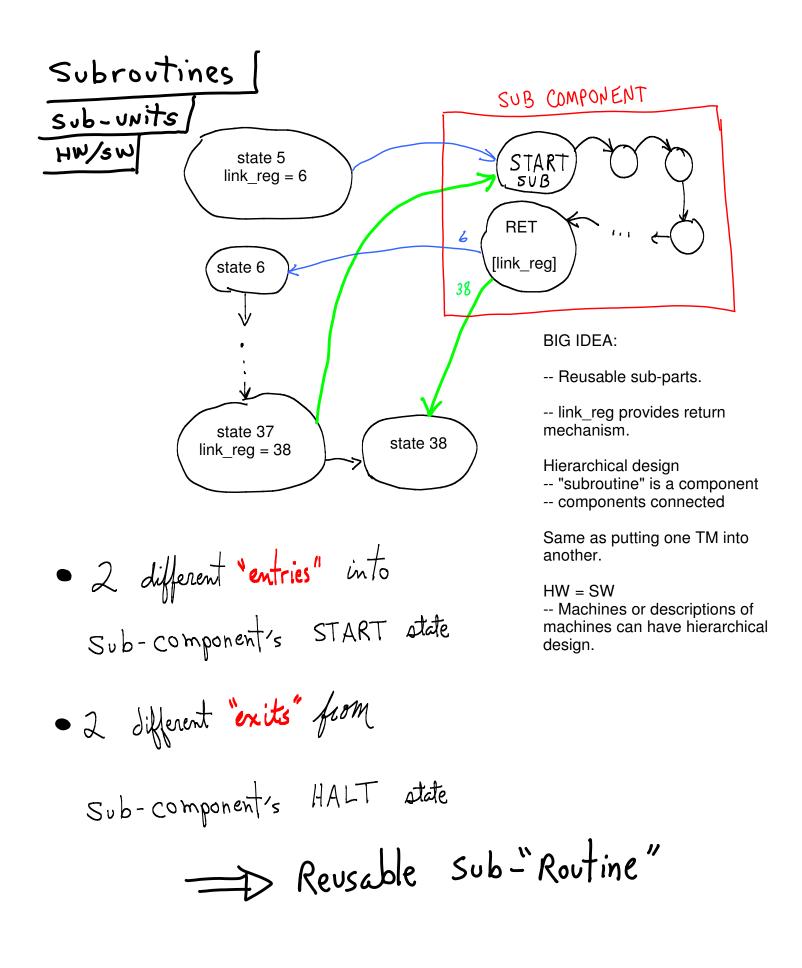

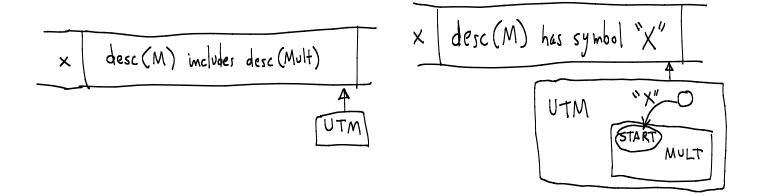

BIG IDEA: Extend simulator with additional hardware (hardware subroutines).

We can add hardware to our computer/simulator:

--- Our description of a machine can have a sub-routine for MULTIPLY,

--- OR, we could add a symbol "X" that causes our simulator/computer to branch to a hardware subroutine: FASTER. Desc(M) is also SMALLER. (\*but is computer then slower?)

-- Software == Hardware

Could we extend the desc(M) in the same way?

Could we have some TM, T, described as part of the description of M?

Perhaps we wouldn't even put desc(T) into desc(M)?

Only put an indicator that desc(T) should be inserted into desc(M)?

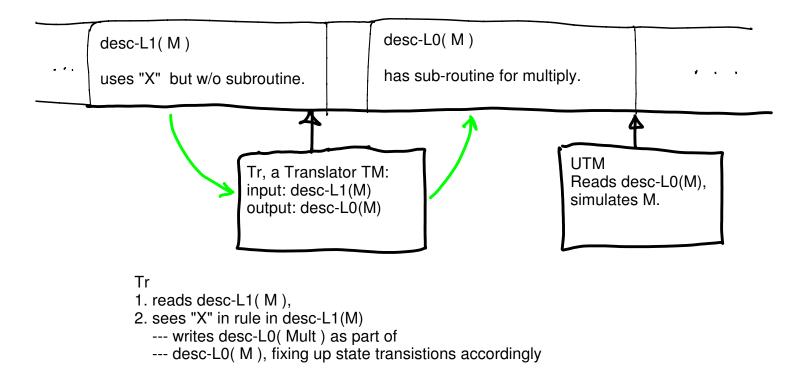

## Hierarchical Translation

L0: "Instruction Set Architecture", ISA, is language of simulating machine, UTM.

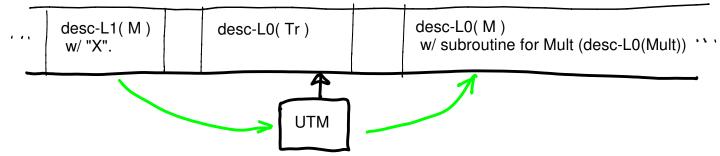

Recall, we only need a description of Tr

UTM simultates Tr, then simulates M. We can,

--- Add levels: desc-L2( M ), and L2-L1 translator.

- --- Eg., scripting language => C++ => C => asm => ISA

- --- Migrate subroutines down to lower levels, eventually into UTM's hardware.

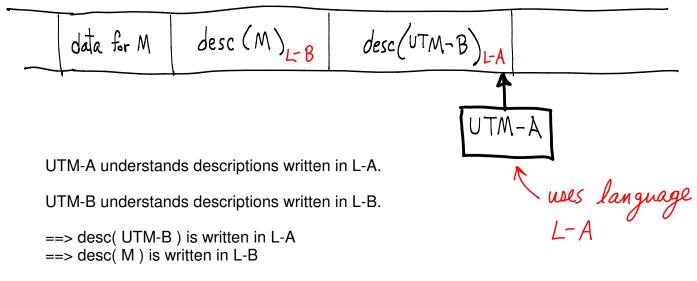

- --- UTM-0 simulates different UTM-1: desc-L0( UTM-1 ), UTM-1 has its own ISA. ==> interpreted languages, JAVA bytecode.

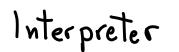

Simulating a UTM? Use UTM-A and desc-LA( UTM-B) ==> Simulate UTM-B simulating M.

UTM-A simulates UTM-B simulating M.

Let's make things even more exciting!

Have symbol "X" in L-Java, keep symbol "X" in L-JVM, have Java-Virtual-Machine jump to desc-LC3( TM-for-symbol-"X") ===> precompiled, faster than simulating OR keep "X" in desc-LC3( TM-for-symbol-"X" ) jump to LC3 hardware-sub-TM-for-symbol-"X" (hardware sub-routine)!