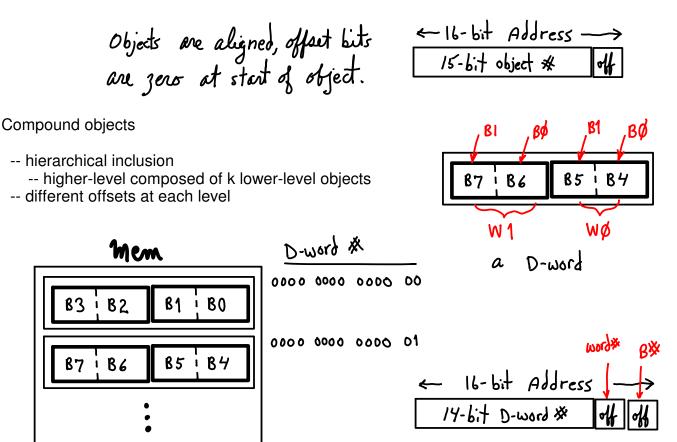

## Memory, addresses, offsets

16-bit addresses

## Mem

Addresses refer to some number of bytes.

How many bytes is determined by the operation's data type.

Native data types

- -- data register size (32-bit, e.g.)

- -- byte operation

- -- half-word operation

- -- word operation

- -- MAR size (40 bits, e.g.)

- -- load word

- -- load double word

- -- load quad word

- -- virtual address (52 bits, e.g.)

- -- page load

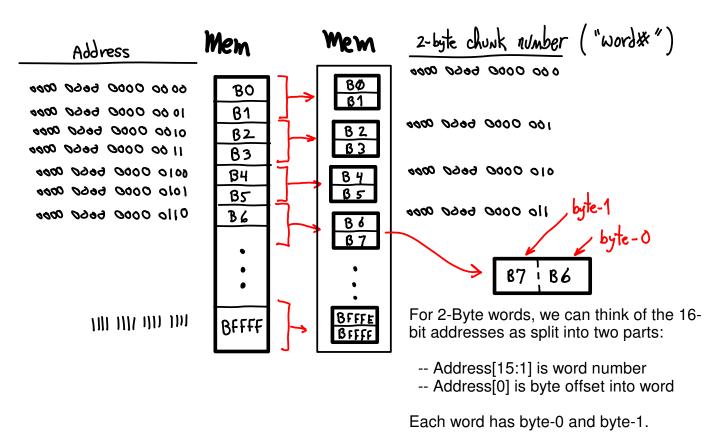

Byte addressable

=

a sequenc d bytes B0 B1 B2 B3 B4 B5 B6

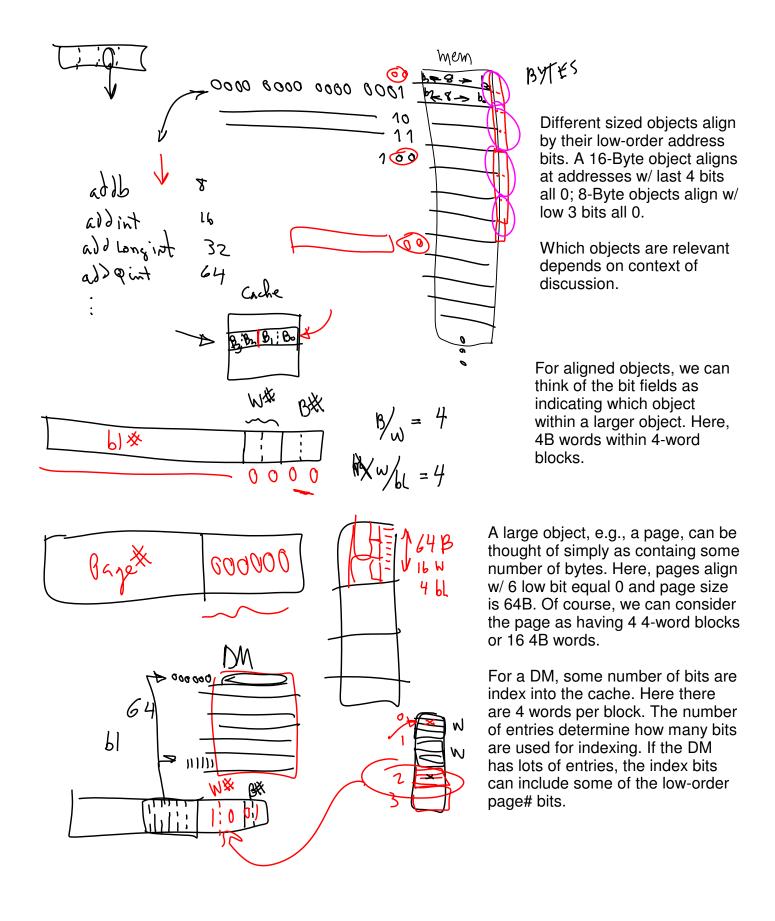

We can view memory as divided up

- -- aligned, non-overlapping chunks

- -- aligned: first byte of first chunk is at x0000, e.g.

- -- non-overlapped: memory is "tiled" by chunks

- -- chunk size depends on what we are interested in

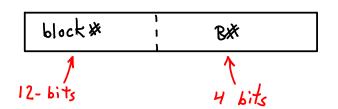

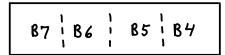

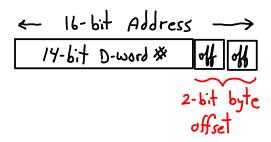

- -- low address bits are offset into chunk

- -- high address bits are chunk number

chunk = Byte

Address Byte\*

in byte addresselle memory, all address bits are used to specify a Byte-sized chunk.

## Mem

| BO         |  |  |  |  |

|------------|--|--|--|--|

| B1         |  |  |  |  |

| B2         |  |  |  |  |

| ВЗ         |  |  |  |  |

| <b>B</b> 4 |  |  |  |  |

| B5         |  |  |  |  |

| B5<br>B6   |  |  |  |  |

|            |  |  |  |  |

| •          |  |  |  |  |

| •          |  |  |  |  |

| '          |  |  |  |  |

| BFFFF      |  |  |  |  |

Of course, we could also see a D-word as composed of bytes.

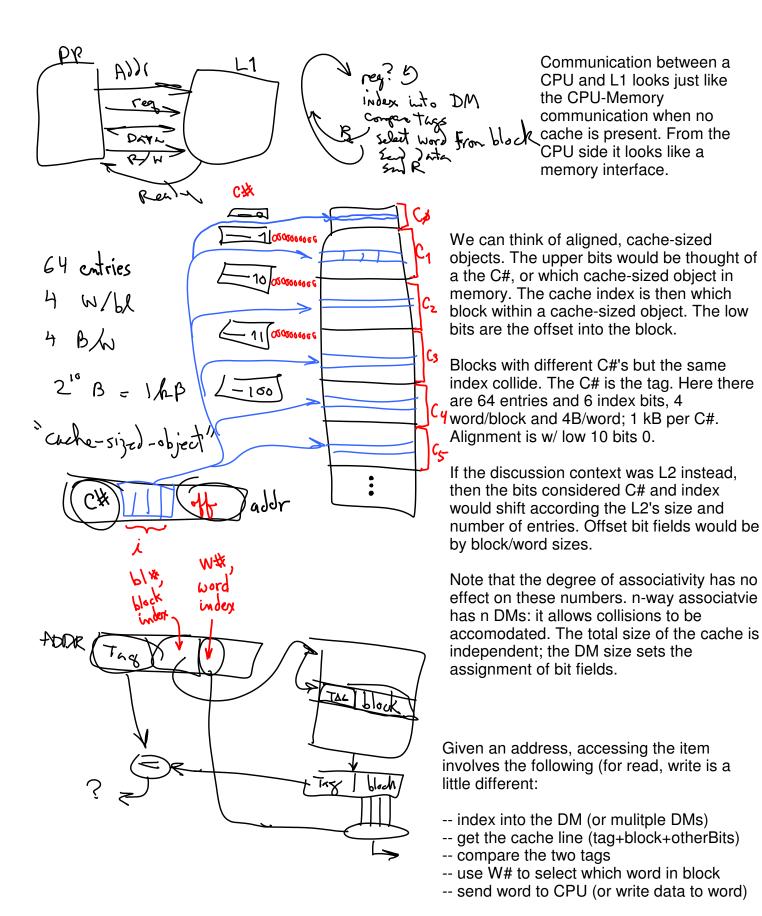

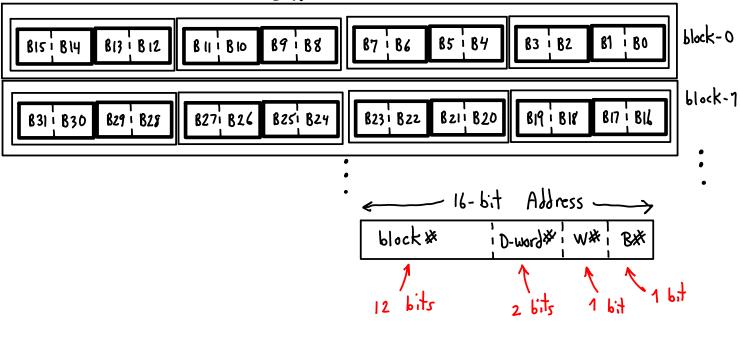

Suppose we have a cache. Say cache blocks are 16 B. We can say a cache block is 4 D-words, or 8 words, or 16 B. We can think of memory divided up into 16 B "cache block-sized" pieces.

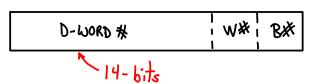

Of course, we can again flatten the hierarchy however we care to. Here the D-word# no longer refers to which D-word in a cache block, but which D-word of the entire memory.

Here, we consider the cache block to be composed only of bytes.