## COSC-520, final exam 2012, spring

NAME:

Open book, open notes (laptops are ok). Partial credit is important; so, explain what you are doing in each question. Do not answer any question with only a number or similar unexplained answer. That will get you very little credit. Show your work, use the back of the pages as needed, but indicate which problem.

**I.** The maximum physically-addressable memory of machine M is 1024-GB (1-TB). M has 64-bit words, 64-bit virtual addresses, and memory is byte-addressable. Pages are 16 kB.

**Q.1.** How many bits wide is a TLB entry for M? Only the minimum number of bits needed to do address translation should be included. Also include 4 bytes of other page table information (such as PID, permissions, and so forth). Because TLB entries are read from memory, round up to an integer number of words.

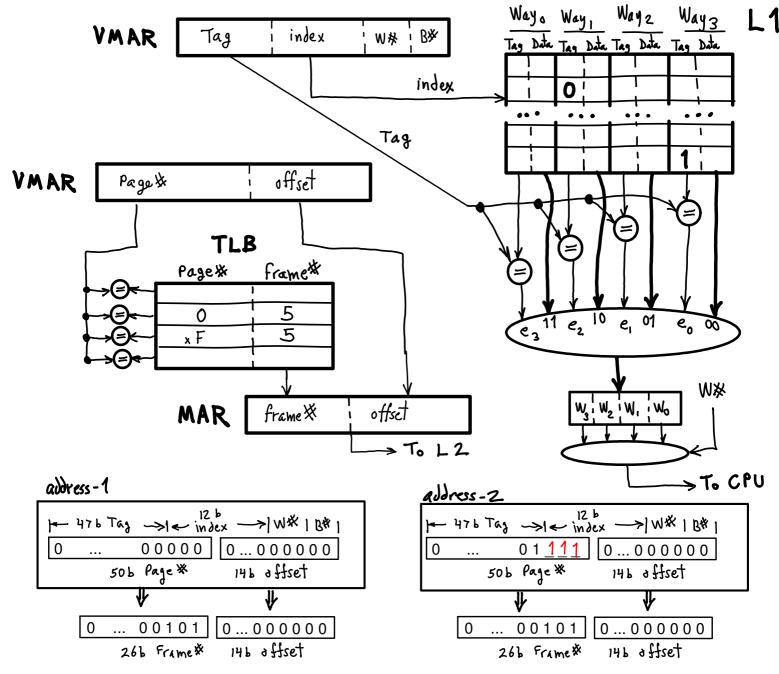

Words are 8B, so we need 3 bits for byte offset, BX. Page is 16 kB, or 2420B, so ffeets are 14 bits and the word offset within a page is 11 bits. Thue, a page 11 3 rumber, PX, is 64-14=50 bits. P# or FX N# BX Physical memory is 2"2"B, or 40 physical address p# FX bits, and a frame number, FX, is 40-14 = 26 bits. A TLB line has (50+26) = 76 bits for address translation, which is 10B after rounding. Total size is (10+4)B, which nounded to whole words (80 word) is 16B (or 2 words).

I (continued). M's L1 cache is virtually indexed, virtually tagged, 4-way set-associative, with 4-word blocks. Its total data size is 512 kB. L2 has 32 MB of data, is 8-way associative, physically indexed and tagged, with 8-word blocks.

Q.2. How many bits wide are L1 and L2 cache entries? Both have 1 valid, 1 dirty, 2 LRU, and 16 PID bits.

17 has 4-word blocks

$$\Rightarrow 2$$

bits for W\$.  $2^{9}2^{10}$  B g data in 4 ways  $\Rightarrow 2^{17}_{4} = 2^{17}$  B pu way.

WMAR Tag index W# B\$ At  $(32B/block)$ , we have  $\frac{2^{17}}{25} = 2^{12}$  entries per

way, ie., 12 index bits:  $64 - (12+2+3) = 47$  hits

for virtual tags. Cache entry in  $(47b + 20b + 32B) = (67b + 256b) = 323b$  per entry.

18 16 3 3 For  $L2$ , we have  $(2^{5}2^{20}B/cache)(\frac{cache}{8 ways}) = 2^{22}B/way$ .

MAR Tag index W# B\$ Blochs are 8 words  $(\frac{8B}{word}) = 64B$  g data per black.

\* entries =  $2^{22}B(\frac{catra}{64B}) = 2^{16}$  entries: 16b index. Tag in 40-(16+3+3) = 18 bits. Total in

(18+20+512)b = (550b per entry).

I (continued). Register \$3 = 0x00000000041FFB8 just before the following instructions are executed:

LW \$11, 0x0(\$3) SUBi \$3, \$3, 0x100000 LW \$12, 0x0(\$3) SUBi \$3, \$3, 0x100000 LW \$13, 0x0(\$3) SUBi \$3, \$3, 0x100000 LW \$14, 0x0(\$3) SUBi \$3, \$3, 0x100000 LF16 \$F2, 0x0( \$3 )

LF16 loads 16B from the memory location specified by 0x0(\$3) into the double-precision floating-point register, \$F2. SUBi subtracts the immediate value from \$3.

.

.

Q.3. What is the address of the low-order 64-bit word accessed by the LF16 instruction (show in hex)?

The starting address in #3 is

$$0 \times 0 \cdots 041 F F B 8$$

and four subtractions of

$(-0 \times 0 \cdots 0100 0 00) \times 4$

yields the low-order word's address:  $0 \times 0 \cdots 001 F F B 8$

Q.4. What is the high-order 8B-word's address? Word boundaries have low 3 bits of address = 0.

We add 1000 (binary) to the address, or  $0 \times 8$  to get

$0 \times 0 \cdots 01 F F C 0$

Q.5. What is the low-order word's L1 cache index? What is its L1 tag? Show in binary and hex. Use "0...0" for repeated hex or binary zeroes.

Q.6. What is the high-order word's L1 cache index? What is its L1 tag?

address in

$$0 \cdots 0 1$$

F F C O (hex)

$0 \cdots 0 0001$  IIII III) 1100 0000 (binary)

Trag index with

index in IIII IIII IIIO (binary) or F F E (hex) Tag in also 0.

**Q.7.** Suppose some block in L1 with index xFFE and tag 0 is valid. Does the LF16 instruction's data access hit or miss in L1?

Q.8. What is the page number for the LF16 instruction's data access?

I (continued). The page table has this entry at index x0...07:

[F# = x1234567 (26 bits), valid = 1, PID = 2367, dirty = 1, LRU = 3, RWX = 100]

**Q.9.** What two L2 indices does the LF16 instruction's data access have? Give binary and hex. What is the L2 tag?

For the low word:

The physical address in

$$\times 1234567$$

concated w/ the low 14 bits of the virtual

address (FFB8): 01 0010 0011 0100 0101 0110 0111 11 1111 1011 1000

w B#

8 word blocks  $\rightarrow 3$ -bit w#, 16-bit index = 0110 0111 1111 1100 or 67FE in hex.

For the high word: Low 14 bits are (FFC0)

01 0010 0011 0100 0101 0110 0111 11 1111 1100 0000

w B#

Index in 67FF. Tag = x12345

**Q.** If L1 misses for both words for the LF16 instruction, and the tag x12345 is not in a valid L2 cache line, how many words of memory must be read from main memory (there is no L3)? How many words of data must be communicated in total (both memory-to-cache and L2-to-L1 reads)? Ignore writing dirty blocks for evicted cache lines and communicating addresses.

Because the access is across an L2 block boundary, and both miss, we must read 2 L2 blocks from memory @ 8 words. We also need to send 2 L1 blocks from L2 @ 4 words. Total is 24 words.

I (conitinued). Shown below are two virtual memory address registers (VMAR). They are the same register with two separate sets of wires tapping its outputs in parallel: one goes directly to L1, the other to the TLB for address translation and then on to L2. The TLB shows that pages 0 and xF map to physical frame 5. L1 shows a valid block with virtual tag 0, and a valid block with virtual tag 1. (Their positions do not indicate their L1 indices.) This is the synonym problem: two virtual addresses refer to the same physical address whose block appears twice in L1. Below is shown an address whose virtual tag is 0 that maps to the same physical word as another address whose tag is 1.

**Q.** Fill in the missing bits for the second address. Suppose we increased the page size to 128 kB, would it be possible for synonyms to have different L1 indices? Why or why not?

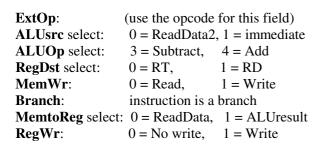

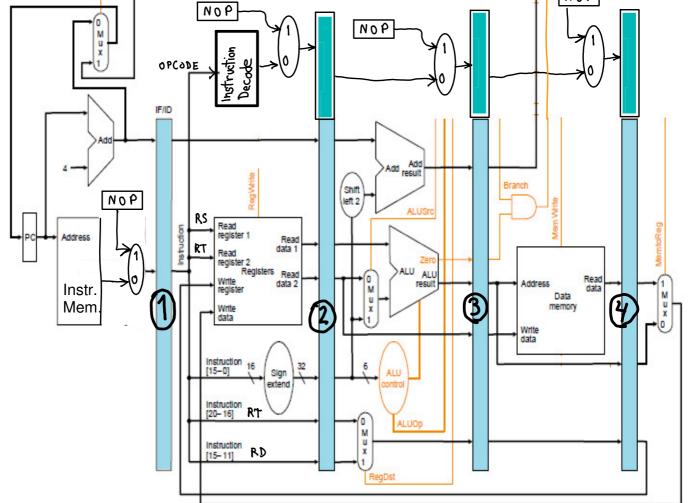

Both addresses are shown as mapping to frame #5 (0...00101). Address-1 has page# =0, address-2 has page\$ > 0. The only mapping shown is from page XF (0...01111); so, 3 one go into missing bits. 128 & B page => 10<sup>7</sup>·10<sup>10</sup> B/page => 17-bit page offset. Because there would be no overlap w/ page\$ (now 47-bit), all synonyms share identical low 17-bits, and 12-bit indices would always match. So, synonyms would always have some index. **II.** Below is shown a 5-stage pipeline architecture (Fetch, Decode, Execute, Memory, and Write-back). Stage registers are the narrow vertical rectangles. At right are instruction formats (high-order bit at the left). Control signals are decoded and then passed through a MUX and written to a pipeline stage register. The control signal destinations are shown as select inputs to datapath MUXs, write-enable signals, and ALU operation control. Branches are taken when the ALU result is 0 (ALU.Zero == 1).

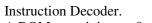

A ROM containing an 8-element word for each opcode. For simplicity, assume 2-bit opcodes: BR==11, LW=10, SW=01, ALU operations=00.

PCSrc

FETCH

DECODE

**Q.** Fill in the missing control signal values in the instruction decoder ROM. A branch is taken if two register values are equal. Branch is an I-format instruction. LW uses RT as its destination register field.

Alusic controls MUX to lower ALU input. LW/SW use immediate value from input 1. ALU and BR use two resister values; so, use imput 0. Reg Dst controls MUX into (3) 0 for RT field a destination and 1 for ND field selects destination. Only LN and ALL ops do reg. write, so others are X · 0 for LW (RT), 1 for ALU (RD). Q. In a crude form, this machine does branch prediction. Does it predict taken or not-taken? What is the misprediction penalty? By fetching in -order below a BR, this is affectively predict not taken. If taken, target address is ready for PC when BR is in Execute (2), but (1) and (2) are about to get incorrectly predicted instructions = 2 NOPs inserted into (1), (2). Q. Suppose a data access (load or store) causes a page fault exception. How many NOPs are injected into the pipeline? Note that the mechanism for jumping to an exception handler is not shown. The address of the exception handler is ready to be written to the PC when LW/SW is in MEM. Instructions after that must be multified to have a precise exception : (1), (2), and (3) need NOPs

written to them: 3 bubbles.

**Q.** Consider an instruction mix of 25% ALU, 30% loads, 20% stores, and 25% branch instructions. What would the average CPI be for this CPU? Assume load-use and branch-delay slots cannot be filled by the compiler; all loads incur a load-use bubble; all branches are taken. There is a two-level cache, and misses stall the pipeline. Instruction fetch and data accesses have an L1 miss rate of 5% and an L2 miss rate of 1%. An L1 miss incurs a 10 cycle L2 delay. An L2 miss incurs an extra 100 cycle delay.

For N instruction fetches, we need I cycle to access from L1, whether we hit or miss. If we miss L1, we need 10 cycles to access L2 whether we hit or miss L2. This happens for N(5%) which min L1. For (1%) of L2 accesses (which are all L1 misses), we miss in L2 and pay another 100 cycles. This happens for N(5%)(1%) of instruction fetches. Fetch cycles = N (1 + (5%) 10 + (5%) (1%) 100). There are N( (30%) + (20%) dota accesses w/ the same cache performance: data access cycles = (0.5)N(1+(5%)10+(5%)(1%)100). BRs cause 2 bubbles each, so for each BR exiting 2 NOPs also exit. There are N(1/4) BR instructions: BR cycles = N(1/4)(1+2). There is no mention made of forwarding. LW can make its read date available for Regfile read when LW is in Write-back (4). Because Ragfile is neg-edge triggered, an instruction needing sate from LW can be in Decode, but 3 and 4 must be NOPS. There are N(20%) LW, LW with w/ 2 NoPs = LW cycles = N(20%)(1+2). are other instructions exit w/o buttles: (SW, ALU) cycles = N(20 ?), (1) + N(307.) (1). Total cycles is sum of above factors:  $C(N) = N(1.5)(1 + (5\%)(10 + (1\%)100)) + N(\frac{1}{4})(3) + N(\frac{1}{5})(3) + N(\frac{1}{2})$  $\overline{CP_{I}} = \frac{C(N)}{N} = \left(\frac{3}{2}\right)\left(\frac{5}{100}\right)\left(11\right) + \frac{3}{2} + \frac{3}{2} + \frac{1}{2} = \frac{3}{2}\left(\frac{1}{20}\right) + \frac{15 + 12 + 10}{20} = \frac{33 + 74}{40} = \frac{110}{40} = 2\frac{3}{4}$

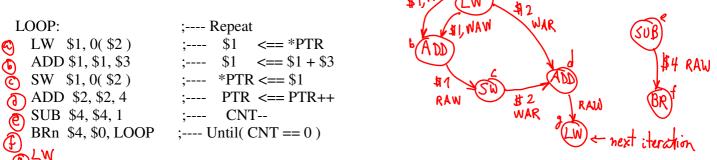

**II** (continued). We have the following loop:

Ben branches if (\$4 - \$0) is not zero, and \$0 always contains 0. So, the branch runs until \$4 reaches 0.

**Q.** Identify all dependencies (RAW, WAR, etc.) and which registers cause them in the above code. Which ones represent pipeline control or data hazards, and how many pipeline bubbles are caused by these hazards?

A-b is a lood-use hazard and w/o forwarding this creates 2 bubbles. b-c is a data RAW hazard and also requires 2 bubbles. e-f is a BR data hazard, also 2 bubbles. Total is 6 bubbles.

**Q.** Reschedule the loop to reduce the number of bubbles as much as possible. You may alter individual instructsions (adjusting offsets). How many bubbles result?

**Q.** Assuming all instruction fetches and data accesses hit in L1, what is the speedup of the rescheduled loop w.r.t. the original loop?

$$S' = \frac{1}{(hew loop cycles)(2R)} = \frac{6+6 NOPS}{6} = 2$$

**Q.** Given the previous question's assumptions, what fraction of the total program's execution would the loop have to represent to attain an overall speedup of 1.25 from this rescheduling?

$$\int_{-1}^{1} = \frac{1}{(1-f) + \frac{f}{2}} = \frac{5}{4} + \frac{1}{2} + \frac{1}{2} + \frac{1}{2} = \frac{4}{5}$$

$$2 - 2f + f = \frac{8}{5} + \frac{1}{2} = \frac{1}{75} + \frac{1}{2} + \frac{1}{75} +$$

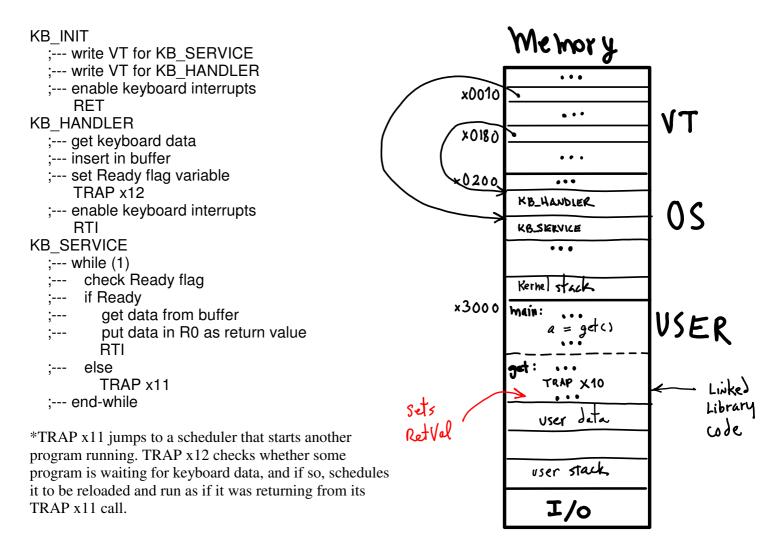

**III.** Joe is working on the OS for the LC3, and has written a device driver for the keyboard. He has also written a service routine that user programs can call to get keyboard input data. The service routine is envoked with "TRAP x10". The interrupt vector for the keyboard is x0180. The service routine is called by a library function "get()" that is assembled separately and linked with the user's C code. Joe's code is shown below (mostly just the comments): The runtime memory map is shown at right. Traps act like exceptions and run in kernel mode. OS space is protected.

**Q**. The C call to get() in user's main() returns a character value into the variable "a". The code generated for this by the compiler uses the C function-call stack protocol. From which stack, kernel or user, would this code get its return value? Where in the above map is the code that puts the return value onto the stack?

The C call is user code; so, return value comes from get ()'s call frame on user's stack. Get () code must set up stack return value, just after TRAP X10 call

**Q**. The call to sleep, "TRAP x11", in KB\_SERVICE, switches contexts to another program, including swapping the entire user memory content. When the sleeping program is awakened, its context has been restored and it is exiting the sleep() trap via RTI. Before sleep() returns, what task must it complete so that RTI and the TRAP x10 call both return corrrectly? Explain.

The kernel stack must have the PC, PSR values that were pushed onto the stack by the TOTAP 11 call. also, the stack needs to be restored so that TRAP x10 calls pushed PC, PSR are below, and the return to user code will work.